Раздел: Документация

0 ... 71 72 73 74 75 76 77 ... 82 говорит о том, что вывод 6 следует присоединить к земле. В строках «Вход» и «Выход» таблиц указаны номера выводов ИС, на которые следует подавать входные импульсы и с которых надлежит снимать выходные. Таблица 14-8

Таблица 14-9

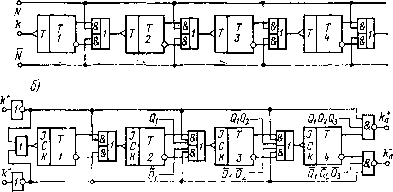

14-4. Реверсивные счетчики Асинхронный реверсивный двоичный счетчик можно построить, если обеспечить подачу сигналов с прямого (при суммировании) или с инверсного (при вычитании) выхода предыдущего триггера на счетный вход последующего. Схема подобного счетчика показана на рис. 14-9, а. В зависимости от сигналов на шинах направления счета N и N цепи И — ИЛИ в меж-триггерных связях обеспечивают работу счетчика в режиме суммирования (N=\) или вычитания (N=\). Действительно, для входного импульса к второго триггера можно записать: Полученное равенство показывает, что при jV=1 k2 = Q\ и обеспечивается режим суммирования, а при /V = 0 k2 = Qi и обеспечивается режим вычитания. Однако асинхронный реверсивный счетчик имеет тот недостаток, что записанный в нем код изменяется при изменении направления счета. Действительно, при переходе, например, от суммирования к вычитанию сигнал на входе последующего триггера будет изменяться с 0 на 1, если предыдущий триггер находится в нуле, и с 1 на 0, если предыдущий триггер стоит в единице. Изменение же потенциала на счетном входе триггера а)  Рис. 14-9. Схемы двоичных реверсивных счетчиков: асинхронною (а) и синхронного (б) с 1 на 0 приведет к его опрокидыванию, т. е. к изменению числа, записанного в счетчике. Синхронный реверсивный двоичный счетчик лишен указанного недостатка. Поскольку на тактовых (счетных) входах всех триггеров синхронного счетчика при отсутствии входных импульсов сигнал равен нулю, то реверсирование в промежутке между этими импульсами не изменит состояния счетчика. Один из вариантов синхронного двоичного реверсивного счетчика показан на рис. 14-9,6. Для большей наглядности на рис. 14-9,6 не показаны все связи между выходами триггеров и входами логических ячеек И — ИЛИ и И — НЕ. Эти связи обозначены путем указания логической функции, которая соответствует сигналу, поданному на один из входов этих Ячеек. Так, например, на входы ячеек И, включенных в цепь И — ИЛИ, установленную между третьим и четвертым триггерами, приходят сигналы k+, Q3 и k~, Q3, и, кроме того, указано, что сюда же следует подвести сигналы Q1Q2 и q1q2. В итоге сигнал k на тактовом входе триггера Т4 определяется соотношением Схема рис. 14-9,6 соответствует счетчику К155ИЕ7. На рис. 14-9,6 не показаны цепи начальной установки этого счетчика, которые совпадают с аналогичными цепями счетчика К155ИЕ6 и будут рассмотрены ниже. На этом рисунке также не указаны номера выводов: они совпадают с номерами подобных выводов счетчика К155ИЕ6 (рис. 14-10-). Как видно из рис. 14-9,6, при приходе импульса на вход суммирования (k+) состояние данного триггера изменяется на противоположное, если все предыдущие триггеры находятся в единице. Точно так же импульс на входе вычитания (k~) опрокинет данный триггер, если все предыдущие находятся в нуле. Аналогичным образом формируются и сигналы переноса при суммировании (к+п) и при вычитании (k-n). Десятичные реверсивные счетчики чаще всего строят, вводя дополнительные Л01 ические связи в двоичные реверсивные счетчики. При этом следует обращать внимание на ТО, чтобы при суммировании и при вычитании одним и тем же числам в счетчике соответствовали одинаковые кодовые группы. На рис. 14-10 показана схема двоично-десятичного синхронного реверсивного счетчика К155ИЕ6, работающего в коде 8-4-2-1. Кроме двоичных реверсивных межтриггерных связей, в счетчике рис. 14-10 существуют дополнительные логические цепи, обеспечивающие недвоичный переход от кода 1001 к коду 0000 при суммировании и обратный переход при вычитании. Как и на предыдущем рисунке, на рис. 14-10 не показаны все логические связи; они заменены указанием логических функций, которые соответствуют сигналам, подаваемым на не-присоединенные входы логических ячеек. Для того чтобы обеспечить недвоичный переход от 1001 к 0000, при суммировании на вход второго триггера пропускается счетный импульс только при QiQ4 = 1, а на вход четвертого триггера — при QiQ2Q3+QiQ4= 1 • Во время вычитания недвоичный переход 0000—1001 обеспечивается благодаря тому, что счетный импульс на вход второго триггера пропускается только при Qi (Q2+Q3+Q4) = 1, а на вход третьего — при QiCMCb+Qs+Q-O =QiQ2(Qs+Q4) = 1. Перенос при сложении формируется тогда, когда QiQ4=l, а при вычитании — когда Q1Q2Q3Q4 = 1 ■ При отсутствии переноса k+n—\ и А-п=1, при переносе сигнал k+n или k~n становится равным нулю на время, определяемое длительностью нулевой фазы входных счетных импульсов. 0 ... 71 72 73 74 75 76 77 ... 82 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||