Раздел: Документация

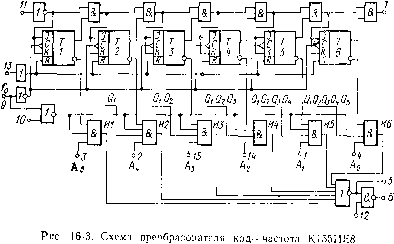

0 ... 76 77 78 79 80 81 82 Для предотвращения сбоев в работе реверсивного счетчика, содержащегося в вычитателе рис. 16-2, б, необходимо предварительно устранить совпадающие импульсы частот fi и f2. Это можно сделать, например, путем привязки импульсов частот f] и f2 к двум последовательностям несовпадающих тактовых импульсов. Подобное тактирование может быть, в частности, произведено с помощью двух устройств, выполненных по схемам рис. 16-1, на тактовые входы которых подаются несовпадающие тактовые импульсы, а иа информационные входы / — импульсы частот f\ и f2. Подобный вычитатель в принципе может быть построен и на одном триггере, иначе говоря, на основе однозарядного реверсивного счетчика. Однако увеличение числа разрядов реверсивного счетчика позволяет упростить последующие цепи при вычитании пульсирующих частот; реверсивный счетчик здесь выполняет функции фильтра нижних частот для частотно-модулированных сигналов. Это дает возможность в ряде случаев устанавливать на выходе вычитателя для подсчета им пульсов разностной частоты простой суммирующий, а не ревер сивный счетчик. Устройство по схеме рис. 16-2,6 может применяться не только как вычитатель частот, но и как фазовый компаратор в системах фазовой автоподстройки частоты и в фазовых системах регулирования скорости электропривода. Если в этих системах устанавливать простейший фазовый компаратор, выполненный на одном триггере, то возможны нежелательные режимы работы (например, настройка на кратную частоту), вы званные тем, что на выходе простейшего компаратора существует сигнал, даже если его входные частоты существенно различны. Применение устройства по схеме рис. 16-2,6 устраняет этот недостаток. Выходное напряжение компаратора (в качестве которого используется среднее значение напряжения с выхода старшего триггера) в данном случае будет изменяться в диапазоне, ограниченном предельными значениями, которые устанавливаются на выходе при неравенстве частот. 16-3. Преобразователи код — частота Преобразователи код — частота (ПКЧ) находят широкое применение в технике частотно-цифрового моделирования и в частотно-цифровых приборах с обратной связью. ПКЧ двоичного кода. На рис. 16-3 показана схема ПКЧ типа К155ИЕ8. Этот ПКЧ содержит шестиразрядный двоичный синхронный счетчик, состоящий из JK-триггеров и ячеек И (эти ячейки расположены в верхней части рис. 16-3). На вход счетчика (вывод 9) подаются тактовые импульсы, следующие с опорной частотой /0- К инверсному выходу каждого триггера присоединена ячейка И (И1—И6), сигнал на выходе которой может быть равен единице только тогда, когда данный триггер находится в нуле, а все предыдущие — в единице. Как видно из рис. 16-3, на входы ячеек И1—И6 подаются также внешние управляющие сигналы Л5—А0. Если Л5 = Л4 = = ... = Л0=1, то на выходах этих ячеек появляются импульсы, частота которых равна f0/2 для И1, fo/4 для И2 и т. д. На выходе ячейки И6 частота следования импульсов будет /0/26 = = /о/64. Импульсы на выходах этих ячеек не совпадают между собой во времени. Действительно, например, импуЛьс на выходе  ячейки ИЗ появляется тогда, когда все предыдущие триггеры (т. е. первый и второй) находятся в единице, а данный (т. е. третий) — в нуле. А если так, то в этот момент не может появиться импульс на выходе ячейки #2, так как одно из условий его появления — нулевое состояние второго триггера. Импульсы с выходов ячеек И1—И6 суммируются ячейкой ИЛИ — НЕ. Изменяя сигналы на входах А0—Л5, можно изменять выходную суммарную частоту ПКЧ. Если Л0—Л5 — сигналы, соответствующие различным разрядам двоичного числа Л, так что А =А5- 254-Л4 • 24-)-.. .+Л0 • 2°, то зависимость между частотой ПКЧ и числом Л будет следующей: / = Л6 + АЛ+ . . . +лЖ = -(Лв-25 + Л4-2* + . . . 2464 64 . • .4 Л0-2°) =-&~А. 0 64 Таким образом устройство по схеме рис. 16-3 преобразует двоичный код Л5Л4...Л0 в выходную частоту, пропорциональную числу, представленному этим двоичным кодом. ИС типа К155ИЕ8 имеет ряд дополнительных управляющих входов. Сигналом «единица», поданным на вход 13, производится начальная установка счетчика в нуль. Сигнал нуль или единица, поданный на вход //. соответственно разрешает или запрещает работу счетчика. Сигнал «единица» на входе 10 отключает ячейки И1—И6, не прерывая счета. Во время работы ПКЧ должно обеспечиваться #ц#1з#ю=1, где Н — значение сигнала, а цифровой индекс соответствует номеру вывода ИС. Триггеры счетчика К155ИЕ8 срабатывают от отрицательных фронтов входного сигнала. Сигнал на выходе 5 имеет вид отрицательных импульсов (с начальным уровнем, соответствующим сигналу единице), совпадающих по фазе с нулевыми значениями входного сигнала /о- Если #12=1, то сигнал на выходе 6 имеет вид положительных импульсов. Возможно каскадное включение ПКЧ. позволяющее увели чивать число разрядов преобразуемого в частоту двоичного кода. Преобразование в частоту двоично-десятичного кода осуществляется соответственно с применением двоично-десятичных делителей входной частоты /о- При этом нужно, чтобы частотные компоненты, получаемые с выходов логических цепей, присоединенных к различным триггерам этого делителя, соответ ствовали весам двоичных разрядов преобразуемого двоично-десятичного кода. Так, например, если преобразуется в частота двоично-десятичный код 4-2-2-1, то и относительные значения частотных компонентов должны быть равны 4; 2; 2; 1. Такое соотношение между частотными компонентами может быть получено в случае, когда в примененном двоично-десятичном делителе на 10 входных импульсов первый триггер совершит 4 перехода из единицы в нуль и обратно, второй и третий триггеры — по 2 перехода и четвертый триггер — 1 переход. Следует обратить внимание на то, что число переходов триггера не связано с весом представляемого им двоичного разряда в двоично-десятичном коде. Например, в делителе, работающем в двоично-десятичном коде 8-4-2-1 (см. табл. 14-1), первый триггер (вес 1) опрокидывается 5 раз, второй (вес 2) —2 раза, третий (вес 4)— 1 раз и четвертый (вес 8)— 1 раз. Так что на основе двоично-десятичного делителя, работающего в коде 8-4-2-1, может быть построен преобразователь в частоту двоично-десятичного кода 5-2-1-1. Подобный преобразователь с синхронным двоично-десятичным делителем, работающим в коде 8-4-2-1, показан на рис. 16-4. Для большей наглядности в нижней части рис. 16-4 показана также схема счетчика, работающего в коде 5-2-1-1, в котором хранится код числа Л, преобразуемый в частоту 0 ... 76 77 78 79 80 81 82 |