Раздел:

Документация0 ...

109 110 111 112 113 114 115 ...

117 Таблица Б.23. Окончание

№ вывода | Символ | Функциональное назначение |

54 | PDO | Выход фазового компаратора |

55 | SUBC | Выход последовательных данных субкода |

56 | SBCK | Вход сигнала тактирования последовательных данных субкода |

57 | Vss | Общий схемы опорного тактового генератора |

58 | Х1 | Для подключения кварцевого резонатора. Вход |

59 | Х2 | Для подключения кварцевого резонатора. Вход |

60 | Vdd | Для подключения источника питания опорного тактового генератора |

61 | BYTCK | Выход тактового сигнала |

62 | CLDCK | Выход сигнала тактирования кадров субкода (7,35 кГц) |

63 | FCLK | Выход делителя частоты опорного тактового генератора (7,35 кГц) |

64 | IPFLAG | Флаг интерполяции. "Высокий" уровень — интерполяция |

65 | FLAG | Выход сигнала "Флаг ошибки" |

66 | CLVS | Выход схемы синхронизации системы CLV. "Высокий" уровень — захват, "низкий" уровень — грубое управление |

67 | CRC | Выход детектора ошибок в служебных данных. "Низкий" уровень — в субкоде имеются ошибки |

68 | DEMPH | Выход схемы распознавания записи с предыскажениями. "Высокий" уровень — запись с предыскажениями |

69 | RESY | Кадровая синхронизация. "Высокий" уровень — кадровые синхрогруппы определены верно |

70 | RST2 | Вход сигнала сброса для встроенного ЦАП |

71 | TEST | Тестовый вывод |

72 | AVddi | Для подключения источника питания встроенного преобразователя I/U |

73 | OUTL | Выход аудиосигнала. Левый канап |

74 | AVssi | Общий встроенного преобразоватепя I/U |

75 | OUTR | Выход аудиосигнала. Правый канал |

76 | RSEL | Вход сигнала выбора полярности ("высокий" уровень — уровень темного логическая единица, "низкий" уровень - уровень темного логический ноль) |

77 | CSEL | Тестовый вывод |

78 | PSEL | Тестовый вывод |

79 | MSEL | Вход схемы выбора частоты сигнала SMCK. "Высокий" уровень — f = 8,4672, "низкий" уровень — f = 4,2336 |

80 | SSEL | Вход схемы выбора режима выходных данных субкода Q. "Высокий" уровень — данные буферизированы |

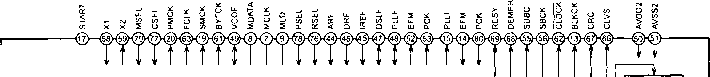

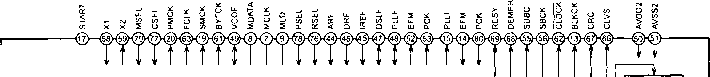

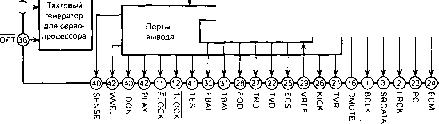

SAA7372

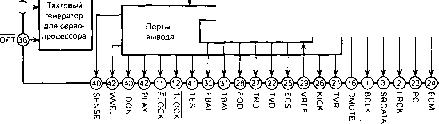

БИС SAA7372 разработана как функционально законченный цифровой сервопроцессор и процессор обработки цифровых сигналов для проигрывателей компакт-дисков. Сервопроцессор базируется на схемотехнических решениях, зарекомендовавших себя в микросхеме TDA1301, а процессор обработки цифровых сигналов повторяет БИС SAA7345, усовершенствованной стратегией коррекции ошибок и расширенными функциональными возможностями.

dvdb, u)

DV5S. (5} RST®-TESTmV

RrDET(38>

Опорный тактовый генератор ГУН для внешнего управления скоростью

АЦП

Интерфейс микроконтроллера

М N66271 OR А

Порты ввода данных

Цифровой се реопро цессор

Система ФАПЧ | | Буфер данных субкода |

| | | |

Е F М-де модул ятор Демодулятор субкода Система кадровой синхронизации

Блок коррекции ошибок

Интерполятор Мягкое

приглушение Цифровой аттенюатор

Система CLV

ЦАП сервосистем

Интергрейс цифрового сигнала

ДеимфазиС

—I—

Цифровой фильтр

ЦАП (1бит)

ШИМ

4—44—44—4

-<7J)rst2

? > > о о

-4-

о с

о*

IX

Основные функции:

•возможность работы в режиме считывания дисков CD-ROM;

. режимы однократной и удвоенной скорости воспроизведения; . наличие режима считывания "lock-to disc" (замыкание на диск);

. полная стратегия коррекции ошибок, реализуемая каждым из декодеров С1 и С2; t = 2 (коррекция до двух ошибок) и е = 4 (коррекция до четырех стираний);

. возможность визуализации на дисплее проигрывателя компакт-дисков полного объема информации пользователя с помощью графического интерфейса;

. наличие всех функций декодера, предусмотренных стандартом, которые реализованы на кристалле БИС с помощью цифровой схемотехники;

. наличие операции маскирования искажений, возникающих при переполнении FIFO-регистра (стековой буферной памяти типа "First-In-First-Out" — "первым вошел — первым вышел") с целью устранения последствий механических воздействий (ударов, вибраций, сотрясений);

•наличие цифрового звукового интерфейса по стандарту EBU (European Broadcasting Union — европейский союз радиовещания), предусматривающий передачу как звуковых данных, так и данных для служебного пользования;

•интегральный цифровой фильтр с двух- и четырехкратной передискретизацией, включающий также режим работы с номинальной частотой дискретизации fs;

. детектирование пиковых значений уровня звуковых данных;

. интерфейс с сокращением разрядности (KILL) звукового сигнала, используемый ЦАП во время цифрового ограничения уровня громкости;

•наличие всех функций сервопроцессора.

I (азначенис выводов — табл. Б.24, структурная схема — рис. Б.24.

Таблица Б.24. Назначение выводов БИС SAA7372

№ вывода | Символ | Функциональное назначение |

1(,> | VsSA1 | Вывод 1 для подключения "аналоговой земли" |

| Vddai | Вывод 1 для подключения источника питания аналоговых схем |

3 | D1 | Вход униполярного тока (вход сигнала диода центрального фотоприемника) |

4 | D2 | Вход униполярного тока (вход сигнала диода центрального фотоприемника) |

5 | D3 | Вход униполярного Тока (вход сигнала диода центрального фотоприемника) |

6 | VRL | Вход эталонного напряжения, необходимого для работы АЦП |

7 | D4 | Вход униполярного тока (вход сигнала диода центрального фотоприемника) |

8 | R1 | Вход униполярного тока (вход сигнала фотодиода дополнительного луча] |

9 | R2 | Вход униполярного тока (вход сигнала фотодиода дополнительного луча) |

10 | IrefT | Вход эталонного тока, необходимого для калибровки АЦП |

11 | Vrh | Вход эталонного напряжения, поступающего от АЦП |

| VsSA2 | Вывод 2 для подключения "аналоговой земли" |

13 | SELPLL | Сигнал, с помощью которого осуществляется выбор одного из умножителей внутренней тактовой частоты, формирующего сигнал, используемый в работе петли ФАПЧ |

14 | ISLICE | Выход тока в петле обратной связи схемы формирования уровней данных |

15 | HFIN | Вход сигнала, поступающего на компаратор |

16(" | Vss A3 | Вывод 3 для подключения "аналоговой земли" |

17 | HFREF | Синфазный вход компаратора |

18 | Iref | Вывод, с которого поступает эталонный ток (при нормальной величине напряжения 0,5Vqd) |

191 | VqDA2 | Вывод 2 для подключения источника питания аналоговых схем |

0 ...

109 110 111 112 113 114 115 ...

117