Раздел: Документация

0 ... 35 36 37 38 39 40 41 ... 117 Таблица. 4.10. Окончание

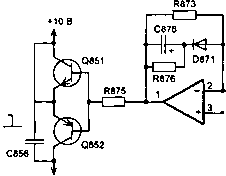

/Для получения необходимого уровня мощности управляющих сигналов, в качестве драйверов также используются мощные операционные усилители, или же к выходу ОУ подключается двухтактный транзисторный каскад, как показано на рис. 4.50. Р103  R871 {zd—<OPEN R872 1 I—С CLOSE ic851 (njm4558l) R874 -10 В Рис. 4.50. Пример схемы управления двигателем привода дископриемника. Позиционные обозначения присвоены согласно CDP JVC XL-Z574BK 4.5. Процессор цифрового сигнала Возвращаясь к процессам, протекающим при декодировании цифрового сигнала, рассмотрим структурную схему DSP CXD2507AQ. В состав БИС входят следующие функциональные устройства (рис. 4.51): •цифровая система ФАПЧ, применяемая для выделения тактовой частоты из воспроизводимого EFM-сигнала; •цифровая система регулирования линейной скорости; •схема кадровой синхронизации и EFM-демодулятор; •схема блочной синхронизации, процессор субкода; •блок обнаружения и коррекции ошибок; •буферная память емкостью 16 Кбайт; •тактовый генератор; •EFM-компаратор и схема контроля асимметрии; •формирователь сигнала для схемы цифрового выхода; •интерфейс цифроаналогового сигнала; •интерфейс процессора системы управления; •устройство формирования последовательности инструкций управления. MNT0(33)« MNT1 (32)" MNT3(3lV WFCKUI)" EMPH@« GFS фу xugf(m>> GTOPfiv XTSL (36] XTAO @ XTAI (3} Интерфейс цифро-аналогового сигнала 7? Формирователь сигнала для схемы цифрового выхода Блок обнаружения и коррекции ошибок Буферная память 16К EFM-демодулятор Схема кадровой синхронизации Процессор субкода CXD2507AQ

EFM-компаратор и схема контроля асимметрии Е § * ? р ш g Цифровая система ФАПЧ 2 § § й * О j о > g tс у = Система регулирования линейной скорости Интерфейс процессора системы управления Процессор формирования последовательности инструкций управления 555 * 2 z Р ш z Рис. 4.51. Структурная схема процессора цифрового сигнала CXD2507AQ Высокочастотный сигнал подается на вывод 14, который является сигнальным входом EFM-компаратора. В целом, схемы компаратора и контроля асимметрии сходны с уже описанными при рассмотрении RF-усилителя CXAI081. Элементы внешнего ФНЧ подключаются к выводам 16 и 17. Последовательность прямоугольных импульсов с выхода EFM-компаратора подается на цифровую систему ФАПЧ. Устройство тактовой синхронизации на основе системы ФАПЧ выделяет тактовую частоту и осуществляет привязку выделенной последовательности прямоугольных импульсов к этой частоте. Далее выходной сигнал схемы тактовой синхронизации, представляющий собой прямоугольные импульсы, длительности которых имеют 9 фиксированных значений, подается на устройство декодирования канального кода. Устройство декодирования канального кода включает в себя схему кадровой синхронизации и EFM-демодулятор. После выделения кадровых синхрогрупп и замены 14-разрядных символов на 8-разрядные последовательность кадров подается в ОЗУ с произвольным доступом. Декодирование помехоустойчивого кода происходит в блоке обнаружения и коррекции ошибок. После завершения процесса декодирования происходит объединение 8-разрядных символов в последовательность 16-разрядных отсчетов левого и правого каналов. Служебная информация обрабатывается процессором субкода. В разделе 1.3 уже было сказано, что в формате Compact Disc Digital Audio из всех служебных каналов используются только каналы Р и Q. С помощью данных, содержащихся в канале Q, реализуется целый ряд потребительских функций, обеспечивается индикация времени каждой дорожки и др. Структура блока данных канала. Q показана на рис. 4.52. 98

Рис. 4.52. Структура блока данных канала Q Две синхрогруппы SO и S1 не являются информационными, а лишь отделяют служебные блоки друг от друга. Четыре бита "Управление" предназначены для характеристики записи на CD — количество каналов и наличие/отсутствие преимфа-зиса. Возможны четыре комбинации: •0000 — двухканальная запись без преимфазиса; •0001 — двухканальная запись с преимфазисом; •1000 — четырехканапьная запись без преимфазиса; •1001 — четырехканапьная запись с преимфазисом. Эти данные используются микроконтроллером для автоматического включения соответствующего режима обработки данных и подключения цепей деимфазиса. Четыре бита "Адрес" обозначают режим заполнения данных канала Q, т.е. содержимого той части блока, которая обозначается как "Данные" (72 бита). Последние 16 бит, обозначенные как "CRC", используются для проверки ошибок. При обнаружении ошибок все данные блока игнорируются как неправильные. Исправление эшибок здесь не производится. В этом и нет необходимости, т.к. блоки многократно повторяются с небольшими изменениями. Как было отмечено выше, содержание данных канала Q определяется кодом адреса. Чаще всего присутствует адрес 0001, определяющий режим 1 заполнения дан- 0 ... 35 36 37 38 39 40 41 ... 117 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||