Раздел: Документация

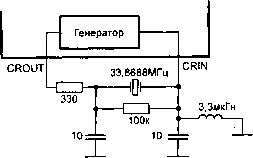

0 ... 61 62 63 64 65 66 67 ... 117 Скорость декодирования и частота кварцевого генератора БИС SAA7370/7370A является прибором, обеспечивающим возможность декодирования с разными скоростями. Такие возможности достигаются за счет использования внутреннего умножителя частоты тактовой синхропоследовательности, построенного на основе использования петли фазовой автоподстройки частоты (ФАПЧ). В зависимости от частоты основного резонанса используемого кварца и от характера внутренних установок, касающихся преобразования основной тактовой частоты (выбор которых осуществляется с помощью регистров В и Е), можно установить одну из двух скоростей воспроизведения, которые показаны в табл. 6.14. Символ "п" здесь отражает кратность увеличения скорости воспроизведения. Таблица 6.14. Скорости воспроизведения

Примечания. На выходе CM I будет частот 22.5792 МГц. на выходе CU6— 33.8688 МГц. на выходе CL4— 8.4672 МГц. только сели сигнал SL-ЛЛЧЛ. = "I" (для SAA7370A). :> Кели используется внешняя тактовая частота 16.9344 МГц и на выходе SRLPLL присутствует 0. то на выходе Cl.l I всегда будет частота 5.6448 МГц. "Для тгих условий представленный набор данных оптимальным не является. Один из имеющихся в наличии внутренних умножителей основной тактовой частоты выбирается с помощью сигнала SELPLL, но такой выбор производится только в тех случаях, когда или используется кристалл кварца с частотой основного резонанса, равной 8,4672 МГц, или керамический резонатор, или тактовая частота вводится в схему от внешнего источника. БИС SAA7370A. Кроме того, позволяет использовать кварцевый резонатор с частотой основного резонанса, равной 16.9344 МГц. Режим "lock-to disc" Для случаев высокоскоростного считывания дисков CD-ROM в БИС SAA7370/A предусмотрен специальный режим "lock-to disc" (замыкание на диск). В этом режиме допускается воспроизведение диска с постоянной угловой скоростью (режим CAV — Constant Angular Velocity), когда скорость поступления входных данных изменяется по мере того как считывающий луч смещается от внутреннего диаметра программной зоны диска к внешнему (скорость потока данных при этом все время возрастает). В таком режиме потребность в FIFO-регистре (стековая буферная память) отпадает, и он блокируется. В этом случае скорость данных на выходе декодера будет зависеть от скорости вращения диска (т.е. от скорости считывания данных с диска). Следовательно, значения синхронизирующих частот (WCLK и SCLK), передаваемых по шине I2S, также будут зависеть от скорости вращения диска. В режиме "lock-to disc" существует предел изменения скорости потока данных в сторону максимума, который определяется скоростными возможностями БИС SAA7370/A (т.е. допустимой максимальной скоростью вращения диска). В любом случае скорость вращения диска должна находиться в пределах диапазона 25-100% ее номинальной величины. Разрешение/запрещение режима "lock-to disc" определяется содержимым регистра Е. Запасные (резервные) режимы В структуру БИС SAA7370/A могут быть заложены два резервных режима. Выбор одного из режимов осуществляется с помощью регистра В (следует отметить, что основа прибора по-прежнему находится в активном состоянии). . Резервный режим 1 — "CD-STOP" (остановка диска). В этом режиме большинство функций (как по входу, так и по выходу) отключено. •Резервный режим 2 — "CD-PAUSE" (прерывание воспроизведения диска). В этом режиме сигналы, характеризующие звуковой выход, отключены, однако петля регулирования и выход сигнала управления двигателем вращения диска остаются в активном состоянии, а через интерфейс продолжается обмен данными субкода. Этот режим иногда называют "Hot Pause" ("Горячая пауза"). Резервные режимы характеризуются наличием на различных выводах следующих сигналов: •МОТ01 и МОТ02 — эти выводы находятся в состоянии высокого импеданса, режим управления — PWM (резервный режим 1 и сброс, осуществляемый из резервного режима 2). Они также переходят в состояние с высоким импедансом во время режима управления PDM (Pulse Density Modulation — модуляция плотностью импульсов) (резервный режим 1 и сброс, осуществляемый из резервного режима 2). •SCL, SDA, S1LD и RAB — сигналы на этих выводах никак не зависят от наличия или отсутствия резервного режима. Нормальное функционирование здесь продолжается. •SCLK, WCLK, DATA, EF, CL11 и DOMB — эти выводы при введении резервных режимов переходят в третье состояние. Нормальное функционирование возобновляется после сброса. •CRIN, CROUT, CL16 и CL4 — сигналы на этих выводах также не связаны с введением резервных режимов, и нормальное их функционирование при этом не нарушается. •VI, V2, V3, V4, V5, CFLG и C2FAIL — так же как и в предыдущем случае, сигналы не связаны с резервными режимами и продолжают нормально функционировать. Генератор тактовых импульсов Схема генератора тактовых импульсов представляет собой традиционную схему на инверторе с двумя выводами, предназначенными для подключения внешнего резонатора, и спроектирована для работы в диапазоне 8-35 МГц. Этот генератор" способен работать с керамическими резонаторами на обеих основных и на третьей дополнительной гармонике кристалла. Для того чтобы подавить колебания на основной частоте кварца и выделить третью гармонику, необходимо использовать внешние компоненты (например, так, как показано на рис. 6.47 и рис. 6.48). Как правило, требуется обеспечить генерацию на частотах 8,4672; 16,9344 или 33,8688 МГц, в зависимости от того, какая внутренняя тактовая частота принята за основную и предусмотрены ли внутренние умножители частоты. SAA7370 CROUT Генератор 330 22 84672МГц -нПг— ЮОк 22 CRIN Рис. 6.47. Подключение внешних компонентов при работе тактового генератора на основной частоте SAA7370  0,001 mk~J~ Рис. 6.48. Подключение внешних компонентов при работе тактового генератора на третьей гармонике Формирователь сигнала данных по уровням и схема регенерации тактовой частоты В структуру БИС SAA7370/7370A интегрирован компаратор, формирующий уровни сигнала данных. Этот компаратор может быть синхронизирован либо тактовой частотой, вырабатываемой кварцевым генератором, либо этой же частотой, но умноженной на 8 (если при использовании частоты кварцевого генератора, равной 8,4672 МГц, сигнал SELPLL имеет "высокий" уровень, а регистр 4 находится в состоянии ОХХХ). Уровни ограничения контролируются с помощью внутреннего источника тока, нагруженного на внешний конденсатор, разряд которого, в свою очередь, регулируется цифровой петлей ФАП (DPLL — Digital Phase-Locked Loop). Регенерация тактовой частоты (частоты следования канальных бит) обеспечивается с помощью внутренней, полностью цифровой петли ФАП. Никаких внешних компонентов данная схема (рис. 6.49) не требует, и выделенная тактовая частота (частота бит) наружу не выводится. Схема ФАП включает в себя два регистра (8 и 9), которые необходимы для установки ширины полосы регулирования и параметров выравнивания. В некоторых случаях требуется наличие сигнала, указывающего на смещение считывающего луча с дорожки. Такой сигнал может быть обеспечен за счет внутреннего соединения с соответствующим элементом схемы сервоуправления (поляр- 0 ... 61 62 63 64 65 66 67 ... 117 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||