Раздел: Документация

0 ... 2 3 4 5 6 7 8 ... 105

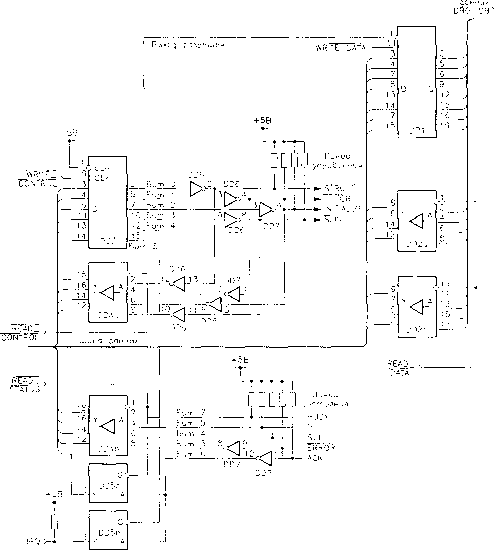

READ STATUS WR)TE CONTRQL READ C0NTR0L Запись В базоВый" адрес + О Чтение из базобоео адреса + Чтение из базобого адреса + Запись В базойа0 адрес + 2 Чтение из базойого адреса + Рис. 1.3. Общая схема параллельного порта с пятым битом регистра управления DD3 (см. рис. 1.3), и порт стал двунаправленным. Следует отметить, что многие параллельные порты, поставляемые со встроенными картами ввода/вывода, двунаправленные. Для любого контакта следует избегать короткого замыкания и/или соединения с шиной питания. Скорость передачи данных через параллельный порт превышает 1 Мб/с. В этой главе детально рассматривается однонаправленный параллельный порт. Контакты порта образуют три группы: данных, управления и состояния. На рис. 1.4 представлена логическая структура параллельного порта. Группа данных Посылает данные от ПК на внешние устройства. Имеет восемь выходных линий и ассоциируется с байтом в адресном пространстве ввода/вывода процессоров х86. Адрес: базовый адрес. Линии интерфейса со сторона компьютеро

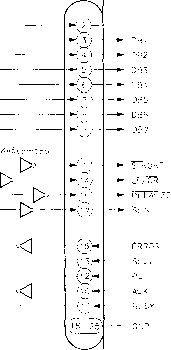

ИнВерторы Линии данных DB0 Линии контроля Компьютер  Линии состояний 25-контактный гнездо5ой разьем D -типа для параллельного порта Рис. 1.4. Логическая структура параллельного порта Группа управления Контролирует внешнее устройство. Имеет четыре инвертированные выходные линии (STROBE, LF/CR, SUN и INITIALIZE). Адрес группы управления: базовый адрес + 2. Группа состояния Группа может использоваться компьютером для получения текущего состояния внешнего устройства, ее адрес: базовый адрес + 1. Имеет пять линий (ERROR, SLCT, РЕ, АСК и BUSY). Линии ERROR и АСК инвертированы, остальные - нет. Назначения регистров параллельного порта приведены в табл. 1.1. Таблица 1.1. Назначения регистров параллельного порта

0 ... 2 3 4 5 6 7 8 ... 105

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||