Раздел: Документация

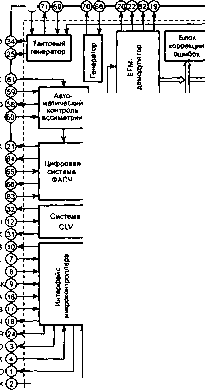

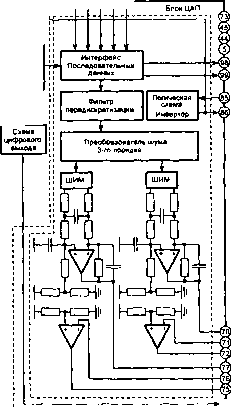

0 ... 97 98 99 100 101 102 103 ... 117 •блок процессора цифрового сигнала (DSP); •цифровые сервосистемы; •цифровой фильтр; •одноразрядный аудио-ЦАП; •аналоговый ФНЧ. Основные функции: •блок процессора цифрового сигнала: •поддержка режима воспроизведения с постоянной угловой скоростью (Constant Angular Velocity); •отсутствие "дрожания" кадров; •возможность режима воспроизведения как с нормальной скоростью, так и с учетверенной; •буферная память объемом 16 К; •EFM-демодулятор; •система кадровой синхронизации; •блок защиты от ошибок реализован с применением суперстратегии; •демодуляция служебных сигналов с устройством обнаружения ошибок в канале субкода Q; •цифровая система сервоуправления двигателем вращения компакт-диска; •схема компенсации асимметрии сигнала; •последовательный интерфейс связи с микроконтроллером; •возможность индикации указателей коррекции ошибок; •формирователь последовательности инструкций управления; •цифровая схема измерения уровня выходного сигнала и его пикового значения; •демодулятор данных CD TEXT; •сервосистема: •полный контроль сервосекции со стороны микроконтроллера; •наличие функций компенсации ухода параметров точной настройки, вызывающих появление ошибок в работе сервосистем; •автоматическое управление усилением каждой сервосистемы; •регулировка баланса F-E, регулировка смещения в схеме усилителя сигнала ошибки фокусировки; •усовершенствованная реализация процедуры выполнения "скачка", позволяющая увеличивать точность нахождения выбранного фрагмента; •одноразрядный ЦАП со встроенным цифровым фильтром: •дополнительный подъем уровня сигналов НЧ; •цифровая схема коррекции предыскажений; •цифровой аттенюатор; •цифровой фильтр с восьмикратной передискретизацией. Рекомендуемое значение напряжения источника питания: VD0= +2,7...5 В (при учетверенной скорости, напряжение питание блока DSP должно быть не менее 4,75 В). Назначение выводов — табл. Б. 15, структурная схема — рис. Б. 15. «О (П т- 2, £. » § S £ > > Й5 FT о г? * 3 dN см to гд I ото. 3 !i s ! х О ш S5" К" со5* Я" § £ б§ 0 м ау о $ о£ ш

ё.вsiа 2£ 5 О2*w ш 5ofсо*w Процессор цифровых данных Процессор данных субкода CXD2588Q/R Процессор, задающий последовательность инструкций управления Блок процессора цифрового сигнала Сарвосекция

Снвмы формирования сигналов MIR, DEFECT. FOK Цифровой сервопроцессор Сервосистема фокусировки Сервосистема отслеживания дорожки записи Сервосистема позиционирования Генератор ШИМ ШИМ Сигнал управления фокусировкой ШИМ Сигнал управления радиальным слежением ШИМ Сигнал управления двигателем позиционирования

5в) Рис. Б.15. Структурная схема БИС CXD2588Q/R Таблица Б.15. Назначение выводов БИС CXD2S88Q/R

0 ... 97 98 99 100 101 102 103 ... 117

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||