...

...

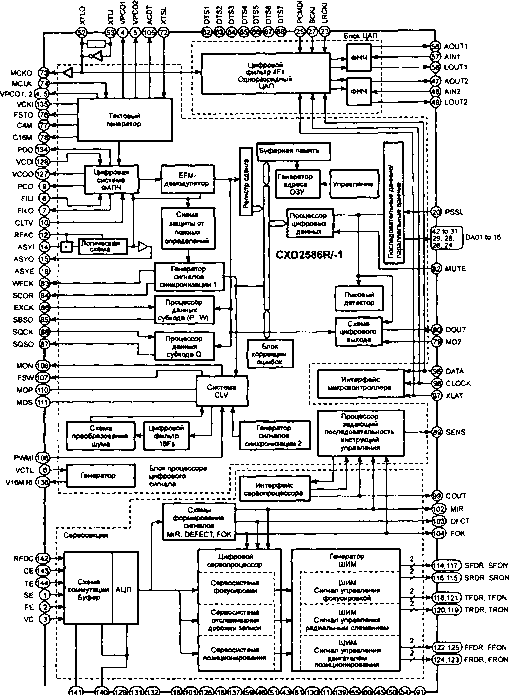

Рекомендуемое значение напряжения источника питания: Vdd - 5 В. Назначение выводов — табл. Б. 13, структурная схема — рис. Б. 13.

8 Щ. "% Тг *» *а 1. "в "я "в "s 1 "Ъ "а *й т, Я \ Ч. "з ь * g 8 8 8* # I8 8 8 8* 58 sf ig$}$ 8

Таблица Б.13. Назначение выводов БИС CXD2586R/-1

№ вывода | Символ | Функциональное назначение |

1 | SE | Вход сигнала ошибки для сервосистемы управления двигателем позиционирования |

2 | FE | Вход сигнала ошибки фокусировки |

3 | VC | Вход схемы формирования средней точки напряжения питания |

4 | VPC01 | Выход схемы с тремя состояниями. Используется при включении ФАПЧ с широкой полосой |

5 | VPC02 | Выход схемы с тремя состояниями. Используется при включении ФАПЧ с широкой полосой |

6 | VCTL | Вход сигнала управления ГУН 2 |

7 | FILO | Выход схемы фильтра основной системы ФАПЧ |

8 | FILI | Вход схемы фильтра основной системы ФАПЧ |

9 | РСО | Выход схемы с тремя состояниями (основная петля ФАПЧ) |

10 | CLTV | Вход управпения основным ГУН |

11 | AVSS1 | Общий аналоговых схем |

12 | RFAC | Вход EFM-сигнала |

13 | BIAS | Для подключения внешнего резистора, задающего ток опорного источника в схеме компенсации асимметрии |

14 | ASYI | Вход компаратора в схеме контроля асимметрии |

15 | ASYO | Выход сигнала EFM преобразованного в двоичный код |

16 | AVDD1 | Для подключения источника питания аналоговых схем |

17 | NC | Нет соединения |

18 | DVddI | Для подключения источника питания цифровых схем |

19 | ASYE | Вход сигнала вкл./откл. схемы компенсации асимметрии (1 — вкл.) |

20 | PSSL | Вход переключения режима выхода аудиоданных (0 — последоватепь-ный, 1 — параллельный) |

21 | WDCK | Выход сигнала тактирования слов данных. 48хВСК, f = 2Fs |

22 | LRCK | Выход сигнала тактирования L/R, f = Fs. В периоде сигнала LRCK — 48 импульсов тактовых сигналов ВСК |

23 | LRCKI | Вход для сигнала тактирования: левый/правый в блоке ЦАП |

24 | DA16 | DA16...DA1 — выходы интерфейса последовательных/параллельных данных. DA16 — выход 16-го разряда (старший разряд) при PSSL = 1 (параллельные данные), при PSSL = 0 выход последоватепьных данных, старший значащий разряд — первый на выходе, 48хВСК |

25 | PCMDI | Вход для аудиоданных в блоке ЦАП (в периоде сигнала LRCK — 48 импульсов тактовых сигналов ВСК) |

26 | DA15 | Выход 15-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала ВСК для режима 48хВСК СЗР — первый на выходе |

27 | BCKI | Вход для сигнапа тактирования битов аудиоданных в блоке ЦАП |

28 | DA14 | Выход 14-го разряда, при PSSL = 1, при PSSL = 0 выход последовательных данных, младший значащий разряд — первый, 64хВСК |

29 | DA13 | Выход 13-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала ВСК для режима 64хВСК МЗР — первый на выходе |

30 | NC | Нет соединения |

31 | DA12 | Выход 12-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала тактирования L/R. В периоде сигнала LRCK — 64 импульса тактового сигнала ВСК |

32 | DA11 | Выход 11-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GTOP (GTOP — сигнал, определяющий состояние схемы кадровой синхронизации, "высокий" уровень свидетельствует о том, что выделенные кадровые синхрогруппы истинны) |

33 | OA10 | Выход 10-го разряда, при PSSL = 1. при PSSL = 0 выход сигнала XUGF (XUGF инвертированная кадровая синхрогруппа) |

Таблица Б. 13. Продолжение

№ вывода | Символ | Функциональное назначение |

34 | DA09 | Выход 9-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XPLCK (XPLCK — инвертированный сигнал тактовой частоты, выделенный из EFM- сигнала) |

35 | DA08 | Выход 8-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GFS ("высокий" уровень сигнала GFS — при условии, что выделенная из EFM-сигнала кадровая синхрогруппа предполагается системой защиты на данном месте, т.е. нет необходимости в коррекции) |

36 | DA07 | Выход 7-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала RFCK (период RFCK = 136 мкс, сигнал характеризует точность кварцевого генератора) |

37 | DA06 | Выход 6-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала С2Р0 (наличие ошибок при считывании данных) |

38 | DA05 | Выход 5-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XRAOF (появление данного сигнала вызвано величиной джиттера, превышающей величину ± 28 кадров, ОЗУ не в состоянии скомпенсировать данную величину) |

39 | DA04 | Выход 4-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT3 |

40 | DA03 | Выход 3-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT2 |

41 | DA02 | Выход 2-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT1 |

42 | DA01 | Выход 1-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT0 |

43 | DVSS1 | Общий цифровых схем |

44 | NC | Нет соединения |

45 | AVSS41 | Общий аналоговых схем |

46 | AVD04 | Для подключения источника питания аналоговых схем |

47 | AOUT2 | Линейный выход второго канала |

48 | AIN2 | Аналоговый вход второго канала |

49 | LOUT2 | Аналоговый выход второго канала |

50 | AVSS42 | Общий аналоговых схем |

51 | AV0D5 | Для подключения источника питания опорного тактового генератора |

52 | XTLO | Выход инвертора в схеме тактового генератора (подключение кварцевого резонатора 33,8688 МГц) |

53 | XTLI | Вход инвертора в схеме тактового генератора (подключение кварцевого резонатора 33,8688 МГц) |

54 | AVSS5 | Общий опорного тактового генератора |

55 | AVSS31 | Общий аналоговых схем |

56 | LOUT1 | Линейный выход первого канала |

57 | AIN1 | Аналоговый вход первого канала |

58 | AOUT1 | Аналоговый выход первого канала |

59 | AVdd3 | Для подключения источника питания аналоговых схем |

60 | AVSS32 | Общий аналоговых схем |

61 | NC | Нет соединения |

62 | DTS1 | Тестовый вывод встроенного ЦАП |

63 | DTS2 | Тестовый вывод встроенного ЦАП |

64 | DTS3 | Тестовый вывод встроенного ЦАП. В схеме проигрывателя обычно не подключен |

65 | DTS4 | Тестовый вывод встроенного ЦАП. В схеме проигрывателя обычно не подключен |

66 | DTS5 | Тестовый вывод встроенного ЦАП. В схеме проигрывателя обычно не подключен |

67 | DTS6 | Тестовый вывод встроенного ЦАП. В схеме проигрывателя обычно не подключен |

...

...