|

|

8(495)909-90-01

8(964)644-46-00

pro@sio.su

|

|

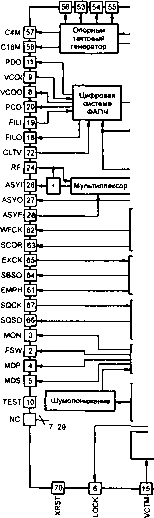

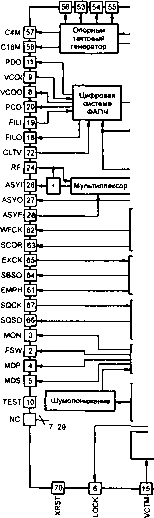

Раздел: Документация0 ... 88 89 90 91 92 93 94 ... 117 Таблица Б.9. Продолжение № вывода | Символ | Функциональное назначение | 8 | VCOO | Выход логической схемы. Используется аналоговой системой ФАПЧ | 9 | VCOI | Аналоговый вход системы ФАПЧ (частота захвата — 8,6436 МГц) | 10 | TEST | Тестовый выход. В схеме проигрывателей подключен к "земле" | 11 | PDO | Выход сигнала аналоговой схемы фазовой автоподстройки | 12 | Vss | Общий | 13 | PWMI | Вход внешнего сигнапа управления скоростью вращения компакт-диска | 14 | V16 | | 15 | VCTL | Вход сигнала управления ГУН 2 в случае использования широкополосной ФАПЧ | 16 | VPCO | Выход схемы с тремя состояниями в схеме широкополосной ФАПЧ | 17 | VCKI | Вход ГУН 2 в случае использования широкополосной ФАПЧ | 18 | FILO | Выход фильтра в схеме умножителя частоты основной системы ФАПЧ | 19 | FILI | Вход фильтра в схемы умножителя частоты основной системы ФАПЧ | 20 | PCO | Выход схемы с тремя состояниями используется основной системой ФАПЧ | 21 | AVss | Общий аналоговых схем | 22 | С LTV | Вход напряжения управления ГУН основной системы ФАПЧ | 23 | AVdd | Для подключения источника питания аналоговых схем (5 В) | 24 | RF | Вход сигнала EFM | 25 | BIAS | Для подключения внешнего резистора, задающего ток опорного источника в схеме компенсации асимметрии | 26 | ASYI | Вход компаратора в схеме контроля асимметрии | 27 | ASYO | Выход сигнала EFM, преобразованного в двоичный вид | 28 | ASYE | Вход сигнала вкл./откл. схемы компенсации асимметрии (1 — вкл.) | 29 | NC | Нет соединения | 30 | PSSL | Вход управления селектора режима выходных аудиоданных (0 — последовательные данные, 1 — параллельные данные) | 31 | WDCK | Выход тактирования слов данных. 48хВСК, f = 2Fs | 32 | LRCK | Выход сигнала тактирования L/R, f = Fs. В периоде сигнала LRCK — 48 импульсов тактового сигнала ВСК | 33 | Vdd | Для подключения источника питания 5 В | 34 | DA16 | DA16...DA1 — выходы интерфейса последовательных/параллельных данных. DA16 — выход 16-го разряда (старший разряд) при PSSL = 1 (параллельные данные), при PSSL = 0 выход поспедовательных данных, старший значащий разряд — первый на выходе, 48хВСК | 35 | DA15 | Выход 15-го разряда, при PSSL = 1, при PSSL = 0 выход сигнапа ВСК для режима 48хВСК СЗР — первый на выходе | 36 | DA14 | Выход 14-го разряда, при PSSL = 1, при PSSL = 0 выход последовательных данных, младший значащий разряд — первый, 64хВСК | 37 | DA13 | Выход 13-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала ВСК для режима 64хВСК МЗР — первый на выходе | 38 | DA12 | Выход 12-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала тактирования L/R. В периоде сигнала LRCK — 64 импульса тактового сигнала ВСК | 39 | DA11 | Выход 11-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GTOP (GTOP — сигнал, определяющий состояние схемы кадровой синхронизации, "высокий" уровень свидетельствует, что выделенные кадровые синхрогруппы истинны) | 40 | DA10 | Выход 10-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XUGF (XUGF инвертированная кадровая синхрогруппа) | 41 | DA09 | Выход 9-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XPLCK (XPLCK инвертированный сигнал тактовой частоты, выделенный из EFM-сигнала) |

Таблица Б.9. Продолжение № вывода | Символ | Функциональное назначение | 42 | DA08 | Выход 8-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GFS ("высокий" уровень сигнала GFS при условии, что выделенная из EFM-сигнала кадровая синхрогруппа, предполагается системой защиты на данном месте, т.е. нет необходимости в коррекции) | 43 | DA07 | Выход 7-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала RFCK (период RFCK = 136 мкс, сигнал характеризует точность кварцевого генератора) | 44 | DA06 | Выход 6-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала С2РО (наличие ошибок при считывании данных) | 45 | DA05 | Выход 5-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XRAOF (появление данного сигнала вызвано величиной джиттера, превышающей величину ± 28 кадров, ОЗУ не в состоянии скомпенсировать данную величину) | 46 | DA04 | Выход 4-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT3 | 47 | DA03 | Выход 3-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT2 | 48 | DA02 | Выход 2-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT1 | 49 | DA01 | Выход 1-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNTO | 50 | APTR | Выход сигнала управления компенсацией апертуры. При использовании правого канала на выводе 50 — логическая 1 | 51 | APTL | Выход сигнала управления компенсацией апертуры. При использовании левого канала на выводе 51 — логическая 1 | 52 | Vss | Общий | 53 | XTAI | Вход инвертора в схеме опорного тактового генератора (подключение кварцевого резонатора 16,9344 МГц или 33,8688 МГц) | 54 | ХТАО | Выход инвертора в схеме опорного тактового генератора (подключение кварцевого резонатора 16,9344 МГц или 33,8688 МГц) | 55 | XTSL | Вход схемы выбора частоты кварцевого резонатора ("низкий" уровень — 16,9344 МГц, "высокий" уровень — 33,8688 МГц) | 56 | FSTT | Выход делителя частоты (2 х 16,9344 МГц): 3 или (2 х 33,8688 МГц): 3 | 57 | FSOF | Выход делителя частоты на 4 (4,2336 МГц) | 58 | С16М | Выход частоты 16,9344 МГц | 59 | MD2 | Вход схемы активизации цифрового выхода ("высокий" уровень — цифровой выход вкл.) | 60 | DOUT | Цифровой выход | 61 | EMPF | Выход сигнала индикации записи CD с преимфазисом (1 — запись производилась с коррекцией АЧХ) | 62 | WFCK | Выход сигнала WFCK (кадровая синхронизация) | 63 | SCOR | Выход детектора синхрогрупп субкода ("высокий" уровень при обнаружении синхрогрупп) | 64 | SBSO | Выход данных субкода P...W | 65 | EXCK | Вход сигнала синхронизации чтения данных субкода Р... W | 66 | SQSO | Выход данных субкода Q | 67 | SQCK | Вход сигнала синхронизации чтения данных субкода Q | 68 | MUTE | Приглушение звука ("высокий" уровень — блокировка) | 69 | SENS | Выход сигналов, согласно запроса микроконтроллера | 70 | XRST | Вход сигнала сброса. Активный уровень — "низкий" | 71 | DATA | Вход последовательных данных от микроконтроллера | 72 | XLAT | Вход сигнала записи от микроконтроллера. Запись последовательных данных происходит по спаду импульса XLAT | 73 | Vdd | Для подключения источника питания 5 В | 74 | CLOCK | Сигнал синхронизации данных, поступающих от микроконтроллера | 75 | SEIN | Вход сигнала SENS. На вывод SEIN подаются сигналы от сервопроцессора, отображающие состояние выходов ряда схем сервосистемы | 76 | CNIN | Вход сигнала подсчета количества дорожек записи при "скачке" |

Таблица Б.9. Окончание № вывода | Символ | Функциональное назначение | 77 | DATO | Выход последовательности инструкций управления для сервопроцессора | 78 | XLTO | Сигнал, по спаду которого происходит загрузка инструкций управления во входной регистр сервопроцессора | 79 | CLKO | Выход сигнала тактирования инструкций управления | 80 | MIRR | Вход сигнала MIRR (определение попожения считывающего пятна между дорожками записи) |

Примечание. Выходные аудиоданные (в двоичном дополнительном коде) передаются в виде пакетов: •в полупериоде сигнала LRCK присутствует 32 импульса ВСК; при этом младший значащий разряд — первый на выходе; •в полупериоде сигнала LRCK присутствует 24 импульса ВСК; при этом старший значащий разряд — первый на выходе. О -J— о - Ю* о {ЭД- CXD2540Q-2 Е 2  ОЗУ 32К Сдвиговый регистр Е FM-двмодулятор Детектор кадровых I синхрогрупп * Защита от ложных определений Синхрогенератор 1 Детектор синхрогрупп субкода Интерфейс данных субкода Обработка данных субкода канала Q. Детектирование ошибок Система CLV | | Кодер приоритетов | | Формирователь адресов запись/чтение | |

Процессор цифровых аудиоданных Обнаружение/ коррекция ошибок Цифровой фильтр системы CLV Генератор Синхрогенератор 2 -0- 2  Вывод данных Параллельные данные/ последовательные 4 681 MUTE Пиковый детектор Формирование последовательности для цифрового выхода Интерфейс микроконтроллера •{ 60 DOUT {ЩМР2 (л] DATA {74] CLOK 41 XLAT Формирователь последовательности инструкций управления 8 S 5 i <75Ц69Н76Н80Ь  0 0 ... 88 89 90 91 92 93 94 ... 117

|

|