...

...

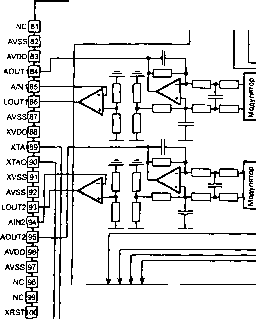

Рис. Б.7. Структурная схема БИС CXD2519Q

Таблица Б.7. Назначение выводов БИС CXD2519Q

№ вывода | Символ | Вход/ выход | Функциональное назначение |

1 | Vdd | | Для подключения источника питания 5 В |

2 | Vss | | "Земля" |

3 | LMUT | 0 | Выход схемы обнаружения отсутствия аудиоданных в левом канале. Блокировка звука в левом канале |

4 | RMUT | 0 | Выход схемы обнаружения отсутствия аудиоданных в правом канале. Блокировка звука в правом канале |

5 | ACDT | 0 | Тестовый выход. Не используется |

6 | CKOUT | 0 | Выход делителя частоты опорного тактового генератора |

7 | SQCK | I | Вход сигнала синхронизации чтения данных субкода Q |

8 | SQSO | 0 | Выход данных субкода Q |

9 | SENSE | 0 | Выход сигналов согласно запроса микроконтроллера |

10 | DATA | I | Вход последовательных данных от микроконтроллера |

11 | XLAT | I | Вход сигнала записи во входной регистр |

12 | CLOK | I | Вход сигнала синхронизации передачи последовательных данных от микроконтроллера |

13 | SEIN | I | Вход сигнала SENS. На вывод SEIN подаются сигналы от сервопроцессора, отображающие состояние выходов ряда схем сервосистемы |

14 | CNIN | I | Вход схемы подсчета количества дорожек записи |

15 | DATO | 0 | Выход последовательности инструкций управления для сервопроцессора |

16 | XLTO | о | Сигнал, по спаду которого происходит загрузка инструкций управления во входной регистр сервопроцессора |

17 | CLKO | 0 | Выход сигнала тактирования инструкций управления |

.18 | SPOA | I | Дополнительный интерфейс микроконтроллера (вход А) |

19 | SPOB | I | Дополнительный интерфейс микроконтроллера (вход В) |

20 | SPOC | I | Дополнительный интерфейс микроконтроллера (вход С) |

21 | SPOD | I | Дополнительный интерфейс микроконтроллера (вход D) |

22 | XLON | 0 | Дополнительный интерфейс микроконтроллера. Выход |

23 | FOK | I | Вход сигнала FOK |

24 | Vdd | | Для подключения источника питания 5 В |

25 | Vss | | "Земля" |

26 | MON | 0 | Двигатель вращения диска: вкл./выкл. |

27 | MDP | 0 | Выходной сигнал системы CLV. Обеспечивает управление скоростью вращения в диапазоне захвата схемы плавной регулировки |

28 | MDS | 0 | Выходной сигнал системы CLV. Обеспечивает разгон и подтормаживание компакт-диска и вывод его на обороты, соответствующие диапазону захвата схемы плавной регулировки |

29 | LOCK | 0 | Сканирование состояния сигнала GFS с частотой 460 Гц |

30 | PWMI | | Дополнительный вход в схеме управления двигателем вращения диска |

31 | TESO | | Тестовый вывод. В схеме проигрывателя не используется |

32 | TES1 | | Тестовый вывод. В схеме проигрывателя не используется |

33 | VP С 02 | 0 | Выход схемы с тремя состояниями. Используется при включении ФАПЧ с широкой полосой |

34 | VPC01 | 0 | Выход схемы с тремя состояниями. Используется при включении ФАПЧ с широкой попосой |

35 | VCKI | I | Вход ГУН 2. Используется при необходимости широкополосной ФАПЧ |

36 | V16M | 0 | Выход ГУН 2. Используется при необходимости широкополосной ФАПЧ |

Таблица Б.7. Продолжение

№ вывода | Символ | Вход/ выход | Функциональное назначение |

37 | VCTL | I | Вход управляющего напряжения для ГУН 2. Используется при необходимости широкополосной ФАПЧ |

38 | РСО | 0 | Выход основной системы ФАПЧ |

39 | FILO | 0 | Выход схемы фильтра основной системы ФАПЧ |

40 | FILI | I | Вход схемы фильтра основной системы ФАПЧ |

41 | AVss | | Аналоговая "земля" |

42 | С LTV | I | Вход управляющего напряжения для основного ГУН |

43 | AVdd | | Для подключения источника питания 5 В. Питание аналоговых схем |

44 | RF | I | Вход EFM-сигнала |

45 | BIAS | | Для подключения внешнего резистора, задающего ток опорного источника в схеме компенсации асимметрии |

46 | ASYI | I | Вход компаратора в схеме контроля асимметрии |

47 | ASYO | 0 | Выход сигнала EFM, преобразованного в двоичный код |

48 | ASYE | I | Включение/отключение схемы коррекции асимметрии. Выкл. — "низкий" уровень |

49 | WDCK | 0 | Выход тактирования слов данных. Пакеты 48 бит, f = 2Fs |

50 | LRCK | 0 | Сигнал тактирования: левый/правый каналы. Пакеты последовательных данных по 48 бит, f = Fs |

51 | LRCKI | I | Вход сигнала тактирования: левый/правый |

52 | PCMD | 0 | Выход последовательных аудиоданных. Старший разряд — первый на выходе |

53 | PCMDI | I | Вход последовательных аудиоданных для встроенного ЦАП. Старший разряд — первый на выходе |

54 | BCK | 0 | Сигнал тактирования битов аудиоданных |

55 | BCKI | I | Вход сигнала тактирования битов аудиоданных для встроенного ЦАП |

56 | Vss | | "Земля" |

57 | Vdd | | Для подключения источника питания 5 В |

58 | GTOP | 0 | Выход сигнала GTOP (сигнал, определяющий состояние схемы кадровой синхронизации; "высокий" уровень свидетельствует, что выделенные кадровые синхрогруппы истинны) |

59 | XUGF | 0 | Выход сигнала XUGF (инвертированная кадровая синхрогруппа) |

60 | XPLCK | 0 | Выход сигнала XPLCK (XPLCK инвертированный сигнал тактовой частоты, выделенный из EFM-сигнала) |

61 | GFS | 0 | Выход сигнала GFS ("высокий" уровень сигнала GFS при условии, что выделенная из EFM-сигнала кадровая синхрогруппа, предполагается системой защиты на данном месте, т.е. нет необходимости в коррекции) |

62 | RFCK | 0 | Выход сигнала RFCK (период RFCK = 136 мкс, сигнал характеризует точность кварцевого генератора) |

63 | C2PO | 0 | Выход сигнала С2РО (наличие ошибок при считывании данных) |

64 | XRAOF | 0 | Контроль состояния буферной памяти |

65 | MNT3 | 0 | Внешний контроль блока обнаружения и коррекции ошибок |

66 | MNT1 | 0 | Внешний контроль блока обнаружения и коррекции ошибок |

67 | MNTO | 0 | Внешний контроль блока обнаружения и коррекции ошибок |

68 | XTSL | I | Вход схемы выбора частоты кварцевого резонатора ("низкий" уровень — 16,9344 МГц, "высокий" уровень — 33,8688 МГц) |

69 | FSTT | 0 | Выход делителя 2/3 FKBaou |

70 | C4M | 0 | Выход сигнала 4,2336 МГц |

71 | DOUT | 0 | Выход цифрового сигнала |

72 | EMPH | 0 | Включение режима "Деимфазис" |

...

...