|

|

8(495)909-90-01

8(964)644-46-00

pro@sio.su

|

|

Раздел: Документация0 ... 82 83 84 85 86 87 88 ... 117 последовательный интерфейс связи с микроконтроллером; возможность мониторинга коррекции ошибок, благодаря усовершенствованному интерфейсу связи с микроконтроллером; формирователь последовательности инструкций управления; усовершенствованная реализация процедуры выполнения "скачка", позволяющая увеличивать точность нахождения выбранного фрагмента; цифровая схема измерения уровня выходного сигнала и его пикового значения; интерфейс цифрового выхода. Рекомендуемое значение напряжения источника питания: VDd= +4,5...5,5 В. Назначение выводов — табл. Б.5, структурная схема — рис. Б.5. {ТтЩв} Сдвиговый регистр EFM-демодулятор Детектор кадровых синхрогрупп Защита от ложных определений  ОЗУ 32K 5 CXD2510Q Синхрогенератор 1 Детектор синхрогрупп субкода Интерфейс данных субкода Обработка данных субкода канала Q. Детектирование ошибок Система CLV | | Кодер приоритетов | | Формирователь адресов запись/чтение | |

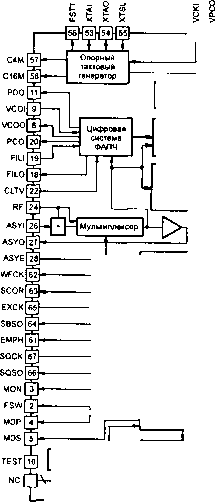

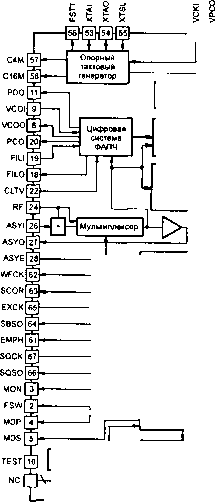

Процессор цифровых аудиоданных Обнаружение/ коррекция ошибок Шумопонижение Цифровой фильтр системы CLV V. 14, 15. 29 {2§—fro)—fj3)-3 8 g Синхрогенератор 2 Вывод данных Параллельные данные/ последовательные данные Пиковый детектор Формирование последовательности для цифрового выхода Интерфейс микроконтроллера -Й-  Формирователь последовательности инструкций управления 450Н51Н32Н31 ir fr и о 4 * 5 §  Н 75Н 69}-j 76Ц 80)Н S 1 О 2 J 30 PSSL 168 MUTE I 71 DATA fr?] CLOK f72lxLAT  77JDATO CLKO 78]XLT0 Рис. Б.5. Структурная схема БИС CXD2510Q

Таблица Б.5. Назначение выводов БИС CXD2510Q № вы-. вода | Символ | Функциональное назначение | 1 | FOK | Вход сигнала FOK. Сигнал FOK подается на микроконтроллер через вывод SENS | 2 | FSW | Выход сигнала переключения постоянной времени в схеме формирования АЧХ системы CLV | 3 | MON | Сигнал включения/отключения двигателя вращения диска | 4 | MDP | Выходной сигнал системы CLV. Обеспечивает управление скоростью в диапазоне захвата схемы плавной регулировки или грубое управление скоростью вращения | 5 | MDS | Выходной сигнал системы CLV. Обеспечивает разгон и подтормажива-ние компакт-диска и вывод его на обороты, соответствующие диапазону захвата схемы плавной регулировки | 6 | LOCK | Сканирование состояния сигнала GFS с частотой 460 Гц | 7 | NC | Нет соединения | 8 | VCOO | Выход логической схемы. Используется аналоговой системой ФАПЧ | 9 | VCOI | Аналоговый вход системы ФАПЧ (частота захвата — 8,6436 МГц) | 10 | TEST | Тестовый выход. В схеме проигрывателей подключен к "земле" | 11 | PDO | Выход сигнала аналоговой схемы фазовой автоподстройки | 12 | Vss | "Земля" | 13 | TESTO | Тестовый выход. В схеме не подключается | 14, 15 | NC | Нет соединения | 16 | VPCO | Выход схемы с тремя состояниями | 17 | VCKI | Вход тактового сигнала от внешнего ГУН | 18 | FILO | Выход схемы фильтра основной системы ФАПЧ | 19 | FILI | Вход схемы фильтра основной системы ФАПЧ | 20 | PCO | Выход схемы с тремя состояниями (используется основной системой ФАПЧ) | 21 | AVss | Аналоговая "земля" | 22 | С LTV | Вход напряжения управления ГУН основной системы ФАПЧ | 23 | AVdd | Для подключения источника питания аналоговых схем (5 В) | 24 | RF | Вход сигнала EFM | 25 | BIAS | Для подключения внешнего резистора, задающего ток опорного источника в схеме компенсации асимметрии | 26 | ASYI | Вход компаратора в схеме контроля асимметрии | 27 | ASYO | Выход сигнала EFM, преобразованного в двоичный вид | 28 | ASYE | Вход сигнала вкл./Откл. схемы компенсации асимметрии (1 — вкл.) | 29 | NC | Нет соединения | 30 | PSSL | Вход управления селектора режима выходных аудиоданных (0 — последовательные данные, 1 — параллельные данные) | 31 | WDCK | Выход тактирования слов данных. 48хВСК, f = 2Fs | 32 | LRCK | Выход сигнала тактирования L/R, f = Fs. В периоде сигнала LRCK — 48 импульсов тактовых сигналов ВСК | 33 | Vdd | Для подключения источника питания 5 В | 34 | DA16 | DA16...DA1 —выходы интерфейса последовательных/параллельных данных. DA16 — выход 16-го разряда (старший разряд), при PSSL = 1 (параллельные данные), при PSSL = 0 пакеты последовательных данных по 48 бит, старший знаковый разряд — первый | 35 | DA15 | Выход 15-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала ВСК для режима 48хВСК СЗР — первый на выходе | 36 | DA14 | Выход 14-го разряда, при PSSL = 1, при PSSL = 0 выход последовательных данных, младший знаковый разряд — первый, 64хВСК | 37 | DA13 | Выход 13-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала ВСК |

Таблица Б.5. Продолжение № вывода | Символ | Функциональное назначение | 38 | DA12 | Выход 12-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала тактирования L/R. В периоде сигнала LRCK — 64 импульса тактового сигнала ВСК | 39 | DA11 | Выход 11-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GTOP (GTOP — сигнал, определяющий состояние схемы кадровой синхронизации, "высокий" уровень свидетельствует, что выделенные кадровые синхрогруппы истинны) | 40 | DA10 | Выход 10-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XUGF (XUGF инвертированная кадровая синхрогруппа) | 41 | DA09 | Выход 9-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XPLCK (XPLCK инвертированный сигнал тактовой частоты, выделенный из EFM-сигнала) | 42 | DA08 | Выход 8-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GFS ("высокий" уровень сигнала GFS при условии, что выделенная из EFM-сигнала кадровая синхрогруппа, предполагается системой защиты на данном месте, т.е. нет необходимости в коррекции) | 43 | DA07 | Выход 7-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала RFCK (период RFCK = 136 мкс, сигнал характеризует точность кварцевого генератора) | 44 | DA06 | Выход 6-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала С2Р0 (наличие ошибок при считывании данных) | 45 | DA05 | Выход 5-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XRAOF (появление данного сигнала вызвано величиной джиттера, превышающей величину ± 28 кадров, ОЗУ не в состоянии скомпенсировать данную величину) | 46 | DA04 | Выход 4-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT3 | 47 | DA03 | Выход 3-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT2 | 48 | DA02 | Выход 2-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT1 | 49 | DA01 | Выход 1-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNTO | 50 | APTR | Выход сигнала управления компенсацией апертуры. При использовании правого канала на выводе 50 — логическая 1 | 51 | APTL | Выход сигнала управления компенсацией апертуры. При использовании левого канала на выводе 51 — логическая 1 | 52 | Vss | Подключен к "земле" | 53 | XTAI | Вход инвертора в схеме тактового генератора (подключение кварцевого резонатора 16,9344 МГц или 33,8688 МГц) | 54 | XTAO | Выход инвертора в схеме тактового генератора (подключение кварцевого резонатора 16,9344 МГц или 33,8688 МГц) | 55 | XTSL | Вход схемы выбора частоты кварцевого резонатора ("низкий" уровень — 16,9344 МГц, "высокий" уровень — 33,8688 МГц) | 56 | FSTT | Выход делителя частоты (2 х 16,9344 МГц): 3 или (2 х 33,8688 МГц): 3 | 57 | FSOF | Выход делителя частоты на 4 (4,2336 МГц) | 58 | C16M | Выход частоты 16,9344 МГц | 59 | MD2 | Вход схемы активизации цифрового выхода ("высокий" уровень — цифровой выход вкл.) | 60 | DOUT | Цифровой выход | 61 | EMPF | Выход сигнала индикации записи CD с преимфазисом (1 — запись производилась с коррекцией АЧХ) | 62 | WFCK | Выход сигнала WFCK (кадровая синхронизация! | 63 | SCOR | Выход детектора синхрогрупп субкода ("высокий" уровень — при обнаружении синхрогрупп) | 64 | SBSO | Выход данных субкода P...W | 65 | ЕХСК | Вход сигнала синхронизации чтения данных субкода P...W | 66 | SQSO | Выход данных субкода Q | 67 | SQCK | Вход сигнала синхронизации чтения данных субкода Q |

0 ... 82 83 84 85 86 87 88 ... 117

|

|