...

...

Таблица Б.З. Продолжение

№ вывода | Символ | Вход/ выход | Функциональное назначение |

36 | DA14 | О | Выход 14-го разряда, при PSSL = 1, при PSSL = 0 выход последовательных данных, младший значащий разряд первый, 64хВСК |

37 | DA13 | О | Выход 13-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала BCK для режима 64xBCK МЗР первый на выходе |

38 | DA12 | О | Выход 12-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала тактирования L/R. В периоде сигнала LRCK —64 импульса тактового сигнала ВСК |

39 | DA11 | О | Выход 11-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GTOP (GTOP — сигнал, определяющий состояние схемы кадровой синхронизации; "высокий" уровень свидетельствует, что выделенные кадровые синхрогруппы истинны) |

40 | DA10 | О | Выход 10-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XUGF (XUGF инвертированная кадровая синхрогруппа) |

41 | DA09 | О | Выход 9-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XPLCK (XPLCK инвертированный сигнал тактовой частоты, выделенный из EFM-сигнала) |

42 | DA08 | О | Выход 8-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GFS ("высокий" уровень сигнала GFS при условии, что выделенная из EFM-сигнала кадровая синхрогруппа, предполагается системой защиты на данном месте, т.е. нет необходимости в коррекции) |

43 | DA07 | О | Выход 7-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала RFCK (период RFCK = 136 мкс, сигнал характеризует точность кварцевого генератора) |

44 | DA06 | О | Выход 6-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала С2Р0 (наличие ошибок при считывании данных) |

45 | DA05 | О | Выход 5-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала XRAOF (появление данного сигнала вызвано величиной джиттера, превышающей величину ± 28 кадров, ОЗУ не в состоянии скомпенсировать данную величину) |

46 | DA04 | О | Выход 4-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT3 |

47 | DA03 | О | Выход 3-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT2 |

48 | DA02 | О | Выход 2-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNT1 |

49 | DA01 | О | Выход 1-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала MNTO |

50 | APTR | О | Выход сигнала управления компенсацией апертуры. При использовании правого канала на выводе 50 — логическая 1 |

51 | APTL | О | Выход сигнала управления компенсацией апертуры. При использовании левого канала на выводе 51 — логическая 1 |

52 | Vss | | Подключен к "земле" |

53 | XTAI | I | Вход инвертора в схеме тактового генератора (подключение кварцевого резонатора 16,9344 МГц или 33,8688 МГц) |

54 | XTAO | О | Выход инвертора в схеме тактового генератора (подключение кварцевого резонатора 16,9344 МГц или 33,8688 МГц) |

55 | XTSL | I | Вход схемы выбора частоты кварцевого резонатора ("низкий" уровень — 16,9344 МГц, "высокий" уровень — 33,8688 МГц) |

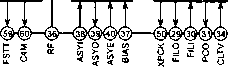

56 | FSTT | О | Выход делителя частоты (2 х 16,9344 МГц) : 3 или (2 х 33,8688 МГц): 3 |

57 | С4М | О | Выход частоты 4,2336 МГЦ |

Таблица Б.З. Окончание

№ вывода | Символ | Вход/ выход | Функциональное назначение |

58 | С16М | О | Выход частоты 16,9344 МГц |

59 | MD2 | О | Вход схемы активизации цифрового выхода ("высокий" уровень — цифровой выход вкл.) |

60 | DOUT | О | Цифровой выход |

61 | EMPF | О | Выход сигнала индикации записи CD с преимфазисом (1 — запись производилась с коррекцией АЧХ) |

62 | WFCK | О | Выход сигнала WFCK (кадровая синхронизация) |

63 | SCOR | О | Выход детектора синхрогрупп субкода ("высокий" уровень — при обнаружении субкода) |

64 | SBSO | О | Выход данных субкода P...W |

65 | ЕХСК | I | Синхронизация чтения данных субкода P...W |

66 | SQSO | О | Выход данных субкода Q |

67 | SQCK | I | Синхронизация чтения данных субкода Q |

68 | MUTE | О | Приглушение звука ("высокий" уровень — блокировка) |

69 | SENS | О | Выход сигналов, согласно запроса микроконтроллера |

70 | XRST | I | Вход сигнала сброса. Активный уровень — "низкий" |

71 | DATA | I | Вход последовательных данных от микроконтроллера |

72 | XLAT | I | Вход сигнала записи от микроконтроллера. Запись последовательных данных происходит по спаду импульса XLAT |

73 | Vdd | | Для подключения источника питания 5 В |

74 | CLOCK | I | Сигнал синхронизации данных, поступающих от микроконтроллера |

75 | SEIN | I | Вход сигнала SENS. На вывод SEIN подаются сигналы от сервопроцессора, отображающие состояние выходов ряда схем сервосистемы |

76 | CNIN | I | Сигнал подсчета количества дорожек записи при "скачке" |

77 | DATO | О | Выход последовательности инструкций управления для сервопроцессора . |

78 | XLTO | О | Сигнал, по спаду которого происходит загрузка инструкций управления во входной регистр сервопроцессора |

79 | CLKO | О | Выход сигнала тактирования инструкций управления |

80 | MIRR | I | Вход сигнала MIRR (определение положения считывающего пятна между дорожками записи) |

Примечание.

•в полупериоде сигнала LRCK присутствует 32 импульса ВСК; при этом младший значащий разряд — первый на выходе;

•в полупериоде сигнала LRCK присутствует 24 импульса ВСК; при этом старший значащий разряд — первый на выходе.

В 80-тивыводном корпусе БИС CXD2508AQ/AR (QFP для версии AQ и LQFP для версии AR) объединены следующие устройства:

•цифровой фильтр и одноразрядный цифроаналоговый преобразователь.

. цифровая система ФАПЧ;

•интерфейс цифрового выхода; . ОЗУ 16 К;

•одноразрядный цифроаналоговый преобразователь. Назначение выводов — табл. Б.4, структурная схема — рис. Б.4.

...

...