Раздел:

Документация0 ...

79 80 81 82 83 84 85 ...

117 Таблица Б.2. Окончание

№ вывода | Символ | Назначение |

64 | DA03 | Выход 3-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала C2F1 |

65 | DA04 | Выход 4-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала C2F2 |

66 | DA05 | Выход 5-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала C2FL |

67 | DA06 | Выход 6-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала С2Р0 |

68 | DA07 | Выход 7-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала RFCK |

69 | DA08 | Выход 8-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала WFCK |

70 | DA09 | Выход 9-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала PLCK |

71 | DA10 | Выход 10-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала UGFS |

72 | DA11 | Выход 11-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала GTOP |

73 | Vdd | Подключен к источнику питания +5 В |

74 | DA12 | Выход 12-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала RAOV |

75 | DA13 | Выход 13-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала C4LR |

76 | DA14 | Выход 14-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала ВСК |

77 | DA15 | Выход 15-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала С210 |

78 | DA016 | Выход 16-го (старшего разряда) при PSSL = 1, при PSSL = 0 выход последовательных данных, старший значащий разряд — первый на выходе, 48хВСК (сигнал DATA) |

79 | WDCK | Тактирование слов. 176,4 кГц - при включенном цифровом фильтре; 88,2 кГц — при выключенном фильтре |

80 | LRCK | Сигнал тактирования: левый/правый каналы (в полупериоде LRCK — 24 импульса ВСК) |

CXD2500BQ

БИС CXD2500BQ разработана как функционально законченный процессор обработки цифровых сигналов для проигрывателей компакт-дисков. Основные функции:

•компенсация широкого диапазона колебаний скорости поступления информации, вызванного неравномерностью вращения CD (±28 кадров), за счет встроенного ОЗУ с произвольным доступом емкостью 32 К;

•формирование с помощью цифровой схемы ФАПЧ тактовой частоты, равной частоте следования бит EFM-кода, которая используется в дальнейшем для стробирования EFM-сигнала;

•система кадровой синхронизации;

•мощная система коррекции ошибок, базирующаяся на принципах улучшенного варианта суперстратегии:

•декодер С1 способен корректировать до двух ошибочных символов;

•декодер С2 способен корректировать до четырех стираний;

- • воспроизведение со скоростями х2, х4, а также возможность плавной регулировки скорости вращения CD;

•система шумопонижения, включаемая во время выполнения "скачков";

•автоматическая блокировка звука в случае, если считывающее пятно пересекает участки зоны записи, на которых отсутствует информация;

•демодуляция служебных сигналов с устройством обнаружения ошибок в канале субкода 0;

цифровая система сервоуправления двигателем вращения компакт-диска (с цифровым фильтром передискретизации);

шестнадцатиразрядный счетчик подсчета количества дорожек записи;

схема компенсации асимметрии сигнала;

последовательный интерфейс связи с микроконтроллером;

формирователь последовательности инструкций управления;

цифровая схема измерения уровня выходного сигнала и его пикового значения;

интерфейс цифрового выхода.

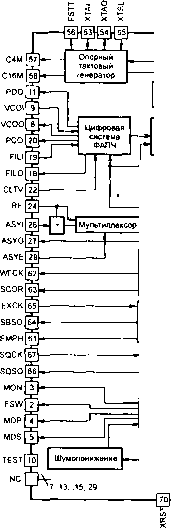

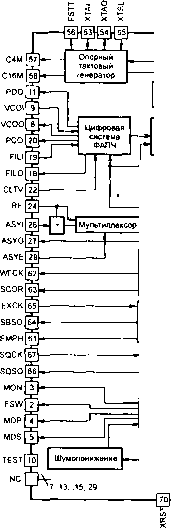

Рекомендуемое значение напряжения источника питания: VDD= +4,75...5,25 В. Назначение выводов — табл. Б.З, структурная схема — рис. Б.З.

о и

ОЗУ 32К

Сдвиговый регистр

Ег"М-демодулятор

Детектор кадровых

синхрогрупп Защита от ложных определений

Синхрогенератор 1 Детектор синхрогрупп субкода

Интерфейс данных субкода

Обработка данных субкода канала Q. Детектирование ошибок

Система CLV

Кодер приоритетов

Процессор цифровых аудиоданных

Обнаружение/ коррекция ошибок

Цифровой фильтр системы

Синхрогенератор 2

-й-

CXD2500BQ

Формирователь

адресов запись/чтение

Вывод данных Параллельные данные/ последовательные данные

Пиковый детектор I

Формирование последовательности для цифрового выхода

Интерфейс микроконтроллера

Формирователь последовательное" и инструкций управления

175Нб9Ц 76Ц80Ц 1

Z fr So!

шиооит

{5Э]МР2 J7l] DATA

{mJclok

J72] XLAT

mjDATO {79JCLKO

Гшхио

Рис. Б.З. Структурная схема БИС CXD2500BQ

Таблица Б.З. Назначение выводов БИС CXD2500BQ

№ вывода | Символ | Вход/ выход | Функциональное назначение |

1 | FOK | I | Вход сигнала FOK. Сигнал FOK подается на микроконтроллер через вывод SENS |

2 | FSW | 0 | Выход сигнала переключения постоянной времени в схеме формирования АЧХ системы CLV |

3 | MON | 0 | Сигнал включения/отключения двигателя вращения диска |

4 | MDP | 0 | Выходной сигнал системы CLV. Обеспечивает управление скоростью в диапазоне захвата схемы плавной регулировки или грубое управление скоростью вращения |

5 | MDS | 0 | Выходной сигнал системы CLV. Обеспечивает разгон и под-тормаживание компакт-диска и вывод его на обороты, соответствующие диапазону захвата схемы плавной регулировки |

6 | LOCK | 0 | Сканирование состояния сигнала GFS с частотой 460 Гц |

7 | NC | | Нет соединения |

8 | VCOO | О | Выход логической схемы. Используется аналоговой системой ФАПЧ |

9 | VCOI | I | Аналоговый вход системы ФАПЧ (частота захвата — 8,6436 МГц) |

10 | TEST | 0 | Тестовый выход. В схеме проигрывателей подключен к "земле" |

11 | PDO | 0 | Выход сигнала аналоговой схемы фазовой автоподстройки |

12 | Vss | | "Земля" |

13...15 | NC | | Нет соединения |

16 | VPCO | | Выход схемы с тремя состояниями |

17 | VCKl | | Вход тактового сигнала от внешнего ГУН |

18 | FILO | 0 | Выход схемы фильтра основной системы ФАПЧ |

19 | FILI | I | Вход схемы фильтра основной системы ФАПЧ 1 |

20 | PCO | | Выход схемы с тремя состояниями (используется основной системой ФАПЧ) |

21 | Avss | | Аналоговая "земля" |

22 | CLTV | I | Вход напряжения управления ГУН основной системы ФАПЧ |

23 | Avdd | | Для подключения источника питания аналоговых схем (5 В) |

24 | RF | I | Вход сигнала EFM |

25 | BIAS | | Для подключения внешнего резистора, задающего ток опорного источника в схеме компенсации асимметрии |

26 | ASYI | I | Вход компаратора в схеме контроля асимметрии |

27 | ASYO | 0 | Выход сигнала EFM, преобразованного в двоичный вид |

28 | ASYE | 1 | Вход сигнала вкл./откл. схемы компенсации асимметрии (1 — вкл.) |

29 | NC | | Нет соединения |

30 | PSSL | 1 | Вход переключения режима выхода аудиоданных (0 — последовательный, 1 — параллельный) |

31 | WDCK | 0 | Выход сигнала тактирования слов данных. 48хВСК, f = 2Fs |

32 | LRCK | | Выход сигнала тактирования L/R, f = Fs. В периоде сигнала LRCK — 48 импульсов тактовых сигналов ВСК |

33 | Vdd | | Для подключения источника питания 5 В |

34 | DA16 | 0 | DA16...DA1 — выходы интерфейса последовательных/ параллельных данных. DA16 — выход 16-го разряда (старший разряд) при PSSL = 1 (параллельные данные), при PSSL = 0 выход последовательных данных, старший значащий разряд — первый на выходе, 48хВСК |

35 | DA15 | 0 | Выход 15-го разряда, при PSSL = 1, при PSSL = 0 выход сигнала ВСК для режима 48хВСК СЗР первый на выходе |

0 ...

79 80 81 82 83 84 85 ...

117