Раздел: Документация

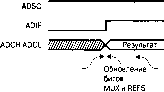

0 ... 130 131 132 133 134 135 136 ... 195 завершается, бит ADSC аппаратно сбрасывается в 0 (в режиме одиночного преобразования), и результат преобразования сохраняется в регистре данных АЦП. Одновременно устанавливается флаг прерывания ADIF регистра ADCSR и генерируется запрос на прерывание. Как и флаги остальных прерываний, флаг ADIF сбрасывается аппаратно при запуске подпрограммы обработки прерывания от АЦП или программно, записью в него лог. 1. Разрешение прерывания осуществляется установкой в 1 бита ADIE регистра ADCSR при установленном флаге I регистра SREG. Если АЦП работает в режиме непрерывного преобразования, то новый цикл начнется сразу же после записи результата. В режиме одиночного преобразования новое преобразование может быть запущено сразу же после сброса бита ADSC (до сохранения результата текущего преобразования). Однако реально цикл преобразования начнется не ранее чем через один такт после окончания текущего преобразования. Временные диаграммы, иллюстрирующие сказанное, приведены на Рис. 9.6. При первом запуске после включения АЦП для выполнения преобразования потребуется 25 тактов, т. е. на 12 тактов больше, чем обычно. В течение этих 12 тактов выполняется «холостое» преобразование, во время которого производится инициализация АЦП (Рис. 9.7). Отдельно следует сказать об использовании режима запуска по прерыванию совместно с дифференциальными каналами. В этом случае АЦП необходимо выключать между преобразованиями, чтобы избежать некорректных измерений, связанных с неопределенностью момента сброса предделителя АЦП. В результате выключения и включения АЦП между преобразованиями будут выполняться только «длинные» преобразования, результаты которых всегда будут корректными. Для формирования тактовой частоты модуля АЦП в нем имеется отдельный предделитель. Коэффициент деления предделителя и соответственно длительность преобразования определяются состоянием битов ADPS2...ADPS0 регистра ADCSRA/ADCSR (см. Табл. 9.5). Наибольшая точность преобразования достигается, если тактовая частота модуля АЦП находится в диапазоне 50...200 кГц. Соответственно, коэффициент деления предделителя рекомендуется выбирать таким, чтобы тактовая частота модуля АЦП находилась в указанном диапазоне. Если же точности преобразования меньше 10 битов достаточно, можно использовать более высокую частоту, увеличивая тем самым частоту выборки. В зависимости от модели выводы микроконтроллера, подключенные/К входу АЦП, определяются состоянием битов MUX3:0, MUX4:0 либо MUX5:0 (MUX5 - в ADCSRB, MUX4...MUX0 - в ADMUX). Для каналов с дифференциальным входом указанные биты определяют также коэффициент предварительного усиления входного сигнала. Соответствие установок этих битов используемым входам АЦП приведено в Табл. 9.6...9.8. Текущее преобразование Следующее преобразование № такта 1 2 3 4 5 6 7 8 9 10 11 12 13 14 I 1 2 ADSC fllllt ADIF ADCH ADCL Результат Обновление Выборка битов MUX и REFS Преобразование завершено а) Текущее преобразование No такта Тактовый сигнал АЦП ш Флаг прерывания 1 I 2 I 3 I 4 I 5 I 6 I 7 I 8 I 9 I 10 11I 12 13 ADATE /~ ADCH ADCL Сброс\ предцелителя Обновление битов MUX и REFS Выборка б) Текущее преобразование Преобразование-завершено Следующее преобразование № такта 11 12 13 1 2 S riilJliT r rL  Преобразование завершено Выборка Обновление битов MUX и REFS Следующее преобразование I 1 I 2 JUL Результат Сброс предцелителя в) Рис. 9.6. Временные диаграммы работы АЦП в режиме одиночного преобразования (а), в режиме запуска по прерыванию (б) и в режиме непрерывного преобразования (в) «Холостое» преобразование Г- № такта 1 2 \ \ 12 Первое преобразование Второе преобразование Тактовый сигнал АЦП aden J" adsc M7t adif adch adclI гг!1-гггишхги1 13 I 14 I 15 I 16 I 17 I 18 I 19 I 20 I 21 I 22 I 23 I 24 I 25 I 26 I 1 2 Обновление битов MUXnREFS Выборка Преобразование завершено I Результат !—т- Обновление битов MUX и REFS Рис. 9.7. Временные диаграммы работы АЦП при первом преобразовании (режим одиночного преобразования) Таблица 9.5. Задание коэффициента деления предделителя АЦП

Таблица 9.6. Управление входным мультиплексором в моделях ATmega8x и ATmega48\/88\/168x

0 ... 130 131 132 133 134 135 136 ... 195 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||