Раздел: Документация

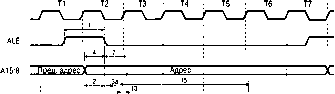

0 ... 45 46 47 48 49 50 51 ... 195 адреса (с помощью битов ХММ2...ХММ0 регистра XMCRB) на соответствующие выводы порта С будут выставлены нули и произойдет обращение к младшим адресам внешнего ОЗУ, начиная с адреса $0000. Ниже приведены два примера программной реализации описанных действий (для микроконтроллера ATmegal28x). Пример на ассемблере ; Константа OFFSET определена как 0x2000 для гарантированного ; обращения к внешней памяти ldi rl6, OxFF out DDRC, rl6; Все выводы порта С - выходы ldi г16, 0x00 out PORTC, г1б; Записали в защелку порта 0x00 ldi rl6, (1«ХММ1) I (1«ХММ0) out XMCRB, rl6; Высвободили биты РС7...5 ldi rl6, ОхАА sts 0x0001+OFFSET, rl6 ; Записали ОхАА по адресу 0x0001 внешней памяти ldi rl6, (0«ХММ1) I (0«ХММ0) out XMCRB, rl6; Переназначили биты РС7...5 ldi rl6, 0x55 sts OxOOOl+OFFSET, rl6 ; Записали 0x55 по адресу (OFFSET+1) ; внешней памяти Пример на Си #defme OFFSET 0x2000 void XRAM examp1e(void) { unsigned char *p = (unsigned char *) (OFFSET + 1); DDRC = OxFF; PORTC = 0x00; XMCRB = (1«XMM1) I (1«XMM0); *p = Oxaa; XMCRB = 0x00; *p = 0x55; } Необходимо помнить, что по сравнению с обращением к внутреннему ОЗУ обращение к внешнему ОЗУ требует, в зависимости от режима, на 1, 2, 3 или 4 такта больше для каждого байта, обрабатываемого командой. Таким образом, время выполнения команд передачи данных (LD, ST, LDS, STS, push и pop) увеличивается на 1, 2, 3 или 4 такта. Если стек расположен во внешнем ОЗУ, то время перехода к обработке прерываний, вызова и возврата из подпрограмм увеличивается на 2, 4, 6, 8, а для моделей ATmega2560x/2561x — на 3, 6, 9 и 12 тактов. Это связано с тем, что во время выполнения указанных операций происходит сохранение или восстановление 16/17-битного счетчика команд и, кроме того, при работе с внешней памятью не используется конвейеризация. Полные временные диаграммы обращения к внешнему ОЗУ с указанием всех параметров сигналов приведены на Рис. 2.26. Значения этих параметров приведены в Табл. 2.22. Тактовый сигнал (clkcpu)  DA7:0 Пред. данныёуАдрес]РЗГ б Ш DA7:0 (ХМВК = 0) RD Данные Данные Примечание. Такты Т5...Т7 присутствуют только при использовании дополнительных тактов ожидания Рис. 2.26. Временные диаграммы обращения к внешнему ОЗУ Таблица 2.22. Динамические параметры сигналов при обращении к внешнему ОЗУ

(продолжение)

0 ... 45 46 47 48 49 50 51 ... 195 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||