Раздел: Документация

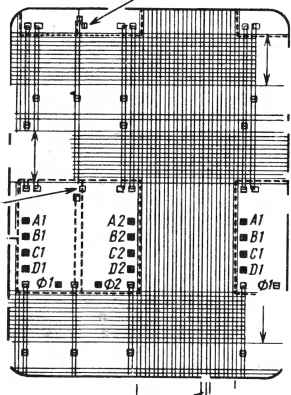

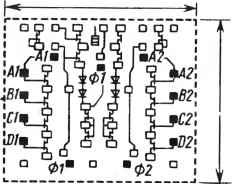

0 ... 72 73 74 75 76 77 78 ких биполярных структур при 300 К должно обеспечивать задержку 10 - 20 пс на вентиль соразмерных с выполненными на кремнии [30]. С другой стороны, были разработаны и достаточно хорошо описаны неоднородные транзисторы, содержащие слои GaAs и AlGaAs, но имеющие структуру полевых транзисторов и называемые обычно транзисторами с высокой подвижностью электронов (ВПЭ-транзисторов) [31]. Эффективная подвижность электронов в канале достигает уровня по крайней мере в 7 - 10 раз выше, чем в обычных полевых транзисторах. Эти структуры на ВПЭ-транзис-торах, каждый длиной 1 мкм, уже продемонстрировали возможность получения задержки примерно 30-40 пс при комнатной температуре и 12,8 пс при 77 К, а также более высоких коэффициентов усиления и проводимости, чем в обычных полевых транзисторах на GaAs. Кроме того, по всей вероятности, арсенид-галлиевые ИС на основе ВПЭ-транзисторов достигнут уровня плотности СБИС уже в этом десятилетии. 26.7. СРАВНИТЕЛЬНЫЙ АНАЛИЗ УЗЛОВ КОММУТАЦИИ, ВЫПОЛНЕННЫХ НА ОСНОВЕ КРЕМНИЯ И АРСЕНИДА ГАЛЛИЯ Подробное сравнение характеристик существующих и ожидаемых арсе-нид-галлиевых транзисторов и вентилей с аналогичными параметрами высокоскоростных кремниевых ЭСЛ-структур может быть поучительным. Например, были произведены оценки характеристик гипотетической заказной ЭСЛ БИС с задержкой менее 1 не, представляющей собой коммутирующий узел в сети ЭВМ с восемью входными и восемью выходными линиями. При современном уровне развития ЭСЛ-технологии такая БИС может быть изготовлена и будет содержать 500 - 700 вентилей. Она будет способна передавать данные от одного или нескольких из восьми входных портов к одному или нескольким из восьми выходных портов со скоростью до 500 Мбит/с на линию при суммарной рассеиваемой мощности ИС около 4 - 8 Вт. Экстраполяция развития технологии до уровня 1985-1987 гг. показывает, что прогрессивные методы литографии позволят при изготовлении таких ЭСЛ-структур приблизительно с тем же числом вентилей вдвое уменьшить мощность рассеивания или вдвое увеличить пропускную способность (т.е. достигнуть скорости в 1 Гбит/с на линию) или частично улучшить и ту и другую характеристики. Такой же коммутационный узел был затем разработан согласно современной технологии арсенид-галлиевых ИС с использованием обоих путей достижения требуемой производительности. Результаты разработки показывают, что в этом случае требуется минимальное число вентилей. При наличии примерно 500 одно компонентных вентилей пропускная способность 1,5 Гбит/с на линию достигается на уровне технологии 1982 г. при рассеиваемой мощности 1,6 Вт (т.е. производительность в 3 раза выше, чем у кремниевых приборов образца 1982 г. при увеличении мощности лишь на 20 - 40%). При последующей более оптимальной реализации такого коммутатора с использованием современной арсенид-галлиевой технологии пропускная способность составила 3 Гбит/с на линию при рассеиваемой мощности 0,3 Вт. Была оценена также ожидаемая производительность арсенид-галлиевых ИС образца 1985- 1987 гг. Предполагается, что технологический параметр составит 0,5-0,7 мкм, при этом производительность возрастает до 4 Гбит/с, а рассеиваемая мощность составит 0,2 Вт. Для арсенид-галлиевой разработки 1985 -1987 гг. была сделана также вторая оценка, но с учетом возможностей ВПЭ-транзисторов с длиной канала 0,9 мкм. Исходя из таких предположений и недавно опубликованных данных можно сделать вывод о реальности создания БИС коммутатора на 500 вентилей со следующими значениями пропускной способности и рассеиваемой мощности: 18 Гбит/с на линию, 0,2 Вт на кристалл; 14 Гбит/с на линию, 0,058 Вт или 10 Гбит/с на линию, 0,015 Вт на кристалл. Другими авторами были опубликованы более скромные результаты, которые экстраполируются до уровня пропускной способности в 8 Гбит/с при 0,048 Вт на кристалл. При достаточно интенсивных исследованиях и проектировании такой рост производительности, по-видимому, будет достигнут в ближайшие 5 лет. 26.8. ВЕНТИЛЬНЫЕ И ЯЧЕЕЧНЫЕ МАТРИЦЫ НА ОСНОВЕ АРСЕНИДА ГАЛЛИЯ Скоростные и мощностные характеристики, описанные в разд. 26.7, подчеркивают некоторые из преимуществ использования арсенид-галлиевой технологии в тех случаях, когда требуется очень малая задержка на вентиль или очень высокая тактовая частота. Однако, как упоминалось ранее, дополнительные трудности, с которыми сталкиваются разработчики высокопроизводительных процессоров сигналов, связаны с их малосерийным производством независимо от того, готовые, заказные или полузаказные ИС использованы в процессоре. Учитывая эту проблему, несколько лабораторий начали разработку универсальных вентильных матриц и (или) базовых матричных кристаллов (ячеечных матриц) на основе арсенида галлия. Отражая результаты, полученные недавно для кремниевых матричных ЭСЛ-кристаллов первого поколения, автор работы [28] указывает на возможность создания арсенид-галлиевых матриц, содержащих 1000 - 4000 эквивалентных вентилей и более. Сравнение максимальной плотности компоновки, достижимой в заказных ИС, и короткого цикла проектирования и изготовления полузаказных ИС на базе вентильных матриц показывает, что второй подход предпочтительнее, если высокая плотность компоновки не требуется или является экономически нецелесообразной. С другой стороны, то, что большая часть площади кристалла отводится на линии связи, не позволяет вентильным (ячеечным) матрицам достичь уровня плотности СБИС в ближайшее время. Действительно, существуют разные мнения относительно целесообразности применения ячеечных GaAs-матриц. Основным отрицательным аргументом при этом является то, что скорость переключения GaAs-транзисторов будет снижаться из-за длинных линий соединений, характерных для матриц такого типа. 26.9. ХАРАКТЕРИСТИКИ АЛГОРИТМОВ ОБРАБОТКИ СИГНАЛОВ, ДЕЛАЮЩИЕ ЦЕЛЕСООБРАЗНЫМ ИХ РЕАЛИЗАЦИЮ НА АРСЕНИД-ГАЛЛИЕВЫХ ВЕНТИЛЬНЫХ (ЯЧЕЕЧНЫХ) МАТРИЦАХ Поскольку в настоящее время в арсенид-галлиевых вентильных (ячеечных) матрицах нельзя достичь уровня интеграции СБИС, естественно возникает вопрос, есть ли смысл использовать их в качестве серьезных конкурентов заказных СБИС, основным достоинством которых является возможность реализации части или полностью центрального процессора на одной СБИС? Должны быть приведены серьезные аргументы, доказывающие возможность и целесообразность использования полузаказных ИС, содержащих лишь 2000- 10 000 вентилей, в аппаратуре высокопроизводительных процессоров сигналов. Ответ на этот вопрос неоднозначен. Во-первых, характеристики алгоритмов обработки сигналов существенно отличаются от характеристик обработки данных по следующим причинам. Операции обработки сигналов обычно производятся над массивами, содержащими очень много элементов. Отдельные элементы этих массивов имеют сравнительно невысокую точность и представлены в виде операндов фиксированной разрядности (8 - 12 разрядов), а в ряде случаев в виде комплексных величин фиксированной разрядности типа Real [12] +Imag [12] и еще реже в виде операндов с блочной запятой или обычных малоразрядных операндов с плавающей запятой [21]. Высокочастотные вычисления с плавающей запятой, требующие сложной аппаратуры, используются крайне редко. Алгоритмы обработки сигналов, разработанные в последние три десятилетия и часто применяемые в различных комбинациях, включают корреляцию, взаимную корреляцию, свертку, быстрое преобразование Фурье, умножение векторов на скаляр, формирование скалярных и векторных произведений, матричные операции и Z-преобразование с ЛЧМ-фильтрацией. Все эти алгоритмы характеризуются: 1) регулярностью элементарных арифметических операций (т.е. операций умножения, сложения и вычитания, с помощью которых они реализуются), 2) ничтожно малым числом условных переходов и 3) большим отношением числа вычислительных операций к числу операций цикла в течение их выполнения. Поэтому большое число общих операций реализовано однообразно. Кроме того, использование двоичных дополнительных кодов фиксированной разрядности позволяет реализовы-вать сложение и вычитание одной элементарной операцией. Обычное умножение операндов фиксированной разрядности в отдельных случаях может быть осуществлено комбинацией двоичных сдвигов, которые даже легче реализовывать [3,32]. Основные Операции обработки сигналов часто связаны друг с другом и образуют цепочку, а внутренняя структура получающихся аппаратных средств также регулярна. Вследствие этого весьма привлекательным является поточное выполнение алгоритмов обработки сигналов с передачей промежуточных результатов от одного этапа к последующему, при котором практически отсутствуют ветвления, циклы или прямая и обратная связи по операндам. Если такие алгоритмические структуры, характеризующиеся небольшой точностью вычислений и относительно невысокой сложностью, реализуют на ИС, то часто можно расположить элементы, выполняющие смежные фрагменты алгоритма, в непосредственной близости друг от друга, что позволяет получить очень короткие линии связи на кристалле. Упомянутый поточный характер алгоритмов позволяет также включать в различные узлы аппаратуры конвейерные регистры, тем самым удваивая или учетверяя скорость работы процессора при данной рабочей частоте с очень незначительным увеличением объема аппаратуры (число вентилей увеличивается обычно лишь на 10 - 20%). Хотя алгоритмы обработки сигналов во многих случаях могут быть распараллелены [3, 33], увеличение объема аппаратуры при этом всегда значительно выше, чем при конвейерной реализации алгоритма, обеспечивающей ту же производительность. Для решения многих задач обработки сигналов можно также использовать так называемую разрядно-модульную организацию их структур, т.е. полный процессор может быть разделен "вертикально" таким образом, что одна ИС, содержащая среднее число вентилей, реализует вычисления над младшими разрядами всех операндов, в то время как связанная с ней соседняя микросхема (часто идентичная ей) или микросхемы реализуют вычисления над старшими разрядами тех же операндов. Этот метод более пригоден для реализации алгоритмов, в которых используются операнды с фиксированной разрядностью или с блочной запятой, чем для решения задач обработки данных с плавающей запятой и высокой точностью. Все сказанное лишь частично касается различий между: 1) большими настраиваемыми вентильными матрицами или ячеечными матрицами со сложностью примерно 1000 - 10000 эквивалентных вентилей и 2) заказными СБИС (хотя и работающими со значительно меньшей скоростью), включающими 10000-50000 вентилей. Хотя очевидно, что сложные кремниевые СБИС должны найти широкое применение в большинстве устройств обработки сигналов, недавние исследования, проведенные в нашей лаборатории, показывают, что обладающий большими возможностями высокопроизводительный процессор сигналов может быть изготовлен на основе настраиваемых вентильных или ячеечных матриц умеренной сложности. В этих исследованиях различные элементы классической структуры обработки сигналов, включая арифметические устройства, порты ввода-вывода, контроллеры памяти, были разработаны на основе макроячеек малой и средней степени интеграции и затем были расчленены на гипотетические вентильные или ячеечные матрицы со сложностью, измеряемой в пределах 1000- 16000 эквивалентных вентилей и с числом выводов корпуса 100-200. Типовые элементы структуры сигнальных процессоров, описанные ранее, включая узлы коммутации, контроллеры памяти и арифметические устройства, могут быть расчленены на вентильные или ячеечные матрицы, содержащие не менее 2000 - 4000 вентилей; для обеспечения ввода-вывода требуется примерно 125 - 185 выводов. Так как сложность базовых матричных кристаллов превышает 4000 эквивалентных вентилей, проблема расчленения в некоторых случаях значительно упрощается и, кроме того, в некоторых случаях минимально требуемое число выводов уменьшается на 15 - 20%. При уровне интеграции в 8000 - 10 ООО вентилей на кристалле могут быть размещены арифметические устройства, реализующие примитивные операции малоразрядных чисел с плавающей запятой, а также операции над комплексными числами с фиксированной запятой. При таком уровне сложности почти все исследованные на сегодня структуры процессоров могут быть реализованы на кристаллах одного типа. Таким образом, вполне реальными являются создание быстродействующего процессора сигналов на основе арсенид-галлиевых ИС с умеренным числом вентилей и появление таких ИС в ближайшее время. 26.10. ТЕХНИЧЕСКИЕ ВОЗМОЖНОСТИ АРСЕНИД-ГАЛЛИЕВЫХ ПРОЦЕССОРОВ БЛИЖАЙШЕГО БУДУЩЕГО В ближайшее время станет технически возможным проектировать и изготавливать арсенид-галлиевые процессоры или смешанные арсенид-галлие-вые и кремниевые процессоры с тактовой частотой 100 МГц и выше. Во-первых, разработано и проверено более 30 различных заказных МИС и СИС 5350 мкм 7675 мкм аааааааааааааааааааааоаааапdddododd о S ooooaooqoaoodddcidooodooonoaaoaoa о g пипмщ,!..,,,,,......,,. о Резервная ячейка ввода-вывода (контактное окно) вв в та вав в шшвш авва а а овв ag а по оишввв па а швав mm □S D а ша □g D ошош о аева евавав пп оваввващвавашв вв в п сз ошвюввш ав в bja. аввввпп в hfo пашвавс riS ашввов „а оввтвв = □ авва ~а am ш иа ад, 0 Её ои а go о" gggS §§ е гт ячеек g§ а- (ьк эквивалентных 2° а о d □ Do □ gBS oS а ago оа Е а о 2 а о «з а а о ag о □□ а аса □а о □Н о оа р оd 5 5о о °о п ао " оog ш da p ш ао J ш аГ а a о a do ю a g° n □ gg в а о g ю a d g Шина r- питаниям Шина земли <Z! 5 каналов s% Резервная ячейка вентилей) (контактное окно) go "Egg ввода-вывода ™" о □ во о 5 5° а о во а о во gn D go о So о Ho о о a о Ho I-I с зо о §o a a оаааоасзоооооооосооаооаоаоааа lol a -*-t- ооааооооооооооооооаооаооо№аооас « питания и земли Внешние контактные площадки 100 * 100м к К внутренней ячейке или от нее Шина земли Выводы для подключения кристалла  \Шина * питания \ Выводы \ \оля подключения шалла ПмкмЗГ  вканалов ц ~Z>8mkm К$нал 2мкм Змкм (Защитная) изолирующая полоса Т вканалов Шина ]пишанил Змкм (Защитная) изолирующая Канал 2 мкм полоса 12 75 мкм каналов  70 мкм Выходная (периферийная) ячейкаВнутренняя ячейка (пара базовых ячеек) Рис. 26.4. Структура арсенид-галлиевой настраиваемой ячеечной матрицы на полевых транзисторах, разрабатываемой в настоящее время (4000 эквивалентных вентилей, задержка распространения 200 пс). Отмечено расположение ячеек и типовых каналов между ними, а также возможность реализации каждой ячейкой различных типов логических схем на GaAs. Процент выхода годных многослойных ИС стал настолько приемлемым, что МИС сейчас включены в экспериментальные образцы процессоров, которые предполагается изготавливать и поставлять [25]. Во-вторых, заказные БИС, содержащие более 1000 вентилей, уже успешно прошли испытания, но процент выхода годных пока неприемлемо мал. Однако и процент выхода годных, и плотность компоновки этих заказных устройств, по-видимому, будут расти подобно тому, как у кремниевых БИС во второй половине 70-х годов. Разрушая упомянутые ранее позиции скептиков относительно целесообразности создания арсенид-галлиевых вентильных и ячеечных матриц, прогресс для этих устройств также становится очевидным. Вентильные и ячеечные матрицы, изготавливаемые как по биполярной И2Л-технологии [28], так и по технологии полевых транзисторов (рис. 26.4), в 1984 г. должны были проходить испытания. Ячеечные матрицы по своей сути более пригодны для высокопроизводительных приборов, особенно на арсенид-галлиевой подложке, поскольку любую вентильную структуру можно поместить в любом желаемом месте на ИС для обеспечения минимального расстояния между источником сигнала и его предполагаемыми приемниками (рис. 26.4). Наконец, такие вентильные или ячеечные матрицы могут оказаться полезными при использовании высокоскоростных биполярных или ВПЭ-структур для увеличения коэффициента разветвления на выходе и пропускной способности ИС. Следовательно, такая комбинация технологий позволяет разрабатывать сверхвысокочастотные, обладающие высокой производительностью процессоры, базируясь в большей степени на "заказных" GaAs ИС, чем на кремниевых СБИС, и в то же время допуская малосерийный выпуск таких устройств и систем. 26.11. СРЕДСТВА АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ, ТРЕБУЕМЫЕ ДЛЯ РАЗРАБОТКИ ПРОЦЕССОРОВ НА ОСНОВЕ АРСЕНИДА ГАЛЛИЯ Для достижения столь высокой производительности арсенид-галлиевых процессоров следующего поколения необходимо предусмотреть соответствующие методы и поддерживающие их средства. Во-первых, обязательным является наличие удовлетворительного испытательного оборудования, а также персонала, имеющего опыт в отладке и разработке высококачественных систем, как и в разработке и осуществлении соответствующего кор-пусирования ИС и в изготовлении многослойных печатных плат. Вследствие очень коротких длин волн, формируемых арсенид-галлиевыми приборами, соединения между компонентами на таких печатных платах должны вести себя как длинные линии (фидеры). Анализ стандартных пакетов программ для трассировки печатных плат показал, что программы, по которым осуществляется разводка без учета требований, предъявляемых к линиям передачи, должны быть модифицированы с учетом особенностей полосковых и микрополосковых линий, присутствующих в многослойных печатных платах [34,35]. 0 ... 72 73 74 75 76 77 78 |