Раздел: Документация

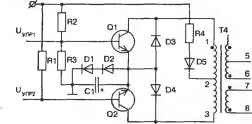

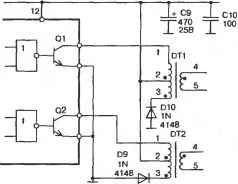

0 ... 8 9 10 11 12 13 14 ... 114 Каскад управления Управление транзисторами полумостового преобразователя осуществляется каскадом на транзисторах Ql, Q2 (рис. 1.29). Кроме этой функции схема управления осуществляет согласование и гальваническую развязку мощных силовых каскадов от маломощных цепей управления. Транзисторы Ql, Q2 схемы работают в ключевом режиме с соединенными эмиттерами поочередно. Коллекторными нагрузками являются полуобмотки трансформатора Т1 (выводы 1-2, 2-3), в среднюю точку которого (вывод 2) подается питание на схему через элементы R4, D5. Диод D5 предотвращает влияние сигналов в первичных обмотках трансформаторов на работу ШИМ-формирователя по шине питания. Резисторы RI, R2 и R3 формируют смещение в цепи базы транзисторов Q2 и Q1 соответственно. Импульсы управления с микросхемы ШИМ-формирователя поступают на базы транзисторов схемы. Под воздействием управляющих импульсов один из транзисторов, например Ql, открывается, а второй Q2, соответственно, закрывается. Надежное запирание транзистора осуществляется цепочкой D1, D2, С1. Так, при протекании тока в открытом транзисторе Q1 по цепи: +25 В -> R4 -> D5 -» Т1(выв. 2-1) -> 01(к-э) -> D2, D1 -> корпус в эмиттере транзистора Q1 формируется падение напряжения +1,6 в. Оно достаточно для запирания транзистора Q2. Наличие конденсатора С1 способствует поддержанию запирающего потенциала во время «паузы». Диоды D3, D4 предназначены для рассеивания магнитной энергии, накопленной полуобмотками трансформатора. Наличие транзисторов в выходном каскаде микросхемы позволяет выполнить эту схему без использования дополнительного транзисторного каскада. На рис. 1.30 показан вариант бестранзисторной схемы, применяемой в источнике питания компьютера «Appis» [2]. Управление транзисторами полумостового преобразователя осуществляется с помощью двух трансформаторов DTI, DT2, являющихся нагрузками выходов микросхемы. Питание к коллекторам выходных транзисторов микросхемы подводится от источника +14 В через средние точки первичных обмоток управляющих трансформаторов. Диоды D9, D10 предназначены для размагничивания сердечников трансформаторов в период закрытого состояния транзистора. Энергия, запасенная трансформатором в период открыто- +2SB  Рис. 1.29. Транзисторный каскад управления го состояния транзистора, при размагничивании подзаряжает конденсаторы фильтров цепи питания. Так, например, при закрытом транзисторе Q1 ток, размагничивающий сердечник DT1, протекает по цепи: DT1(выв. 2) -> С9 -> корпус -> D10 -» ОТ1(выв. 3). Опит =+14В  Рис. 1.30. каскад управления с бестранзисторным управлением Формирователи сигнала Power Good Для корректного запуска вычислительной системы компьютера в системной плате организована задержка подачи питания на время, пока не закончатся переходные процессы в блоке питания и на выходе не установятся номинальные значения выходных напряжений. С этой целью в блоке питания формируется специальный сигнал Power Good («питание в норме»). Задержанный на 0,1...0,5 с сигнал Power Good представляет собой уровень логической единицы, порядка +5 В, который предназначен для начальной установки системной платы. Не менее важной функцией данного формирователя является контроль выходных напряжений в пределах их допуска (табл. 1.9). В табл. 1.20 приведены характеристики сигнала Power Good. Формирователи могут быть выполнены в дискретном и интегральном исполнении. Во втором случае в качестве формирователей нашли применение интегральные компараторы фирм NATIONAL SEMICONDUCTOR CORP и SAMSUNG ELECTRONICS: LM339; KA339 (четыре компаратора в одном корпусе); LM393; КА393 (два в одном корпусе); М51975А. таблица 1.20. типовые характеристики сигнала power good

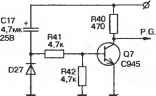

Вариант 1 Формирователь сигнала Power Good источника питания РС-386 [3] показан на рис. 1.31. Формирователь состоит из триггера на транзисторах Q7, Q8, каскада выключения сигнала P.G. на тиристорном эквиваленте Q9, Q10, датчика выходного напряжения Q11 и элементов задержки R41, С27. В исходном состоянии конденсатор С27 пока разряжен, транзистор Q7 закрыт, на его коллекторе потенциал источника питания (шина +5 В), который открывает транзистор Q8. При его отпирании на выход блока передается сигнал логического нуля. По мере формирования выходных напряжений происходит заряд конденсатора С27 от источника напряжения +12 В. Через некоторое время, равное задержке включения, транзистор Q7 открывается, а транзистор Q8 закрывается, на выходе P.G. формируется уровень логической единицы. Суммарное напряжение источников +5 В и +12 В поступает на датчик выходного напряжения, выполненный на резисторах R51, R52. Нормальное напряжение питания не вызывает срабатывания тиристорной структуры Q9, Q10. Выход этих напряжений за пределы установленного допуска приводит к отпиранию транзистора Q1J и протеканию тока по цепи: +ипит -> R46 -> R50 -> 011(э-к) -> R49 R48 -> корпус. Лавинообразный процесс включения транзисторов Q9, Q10 приводит к шунтированию и сбросу сигнала P.G.  Вариант 2 Очень простой вариант исполнения формирователя P.G., встречаемый в источниках питания AT, представлен на рис. 1.32. Схема состоит из элементов задержки на элементах С17, R41, R42 и выходного ключа на транзисторе Q7. С появлением выходного напряжения +5 В по цепи: +5 6-» С17 -» R41 -» R42 -» корпус  протекает ток заряда конденсатора С17. Под воздействием этого тока на резисторах R41, R42 формируется падение напряжения, достаточное для удержания ключа Q7 в открытом состоянии. На выходе линии P.G. напряжение логического нуля. По окончании заряда С17 транзис- Рис. 1.32. Формирователь сигнала торный ключ 07 закрывается и с его кол-Power Good источника AT 0 ... 8 9 10 11 12 13 14 ... 114 |