Раздел: Документация

0 ... 85 86 87 88 89 90 91 ... 105 О READ (чтение); О WRITE (запись); О EWEN (разрешение стирания и записи); О EWDS (запрещение стирания и записи); О ERASE (стирание); О ERAL (стирание всего содержимого); О WRAL (запись всего объема информации).  Зогрузко последовательных донных Выбор микросхемы Выбор способо организации донных  ыгрузко 4 ) последоВ; данных тельных Рис. 7.9. Назначение выводов и логическая схема ST93C56 Рабочий цикл состоит из трех или четырех шагов. Временные диаграммы приведены на рис. 7.10.  Код onepouuu для Розряды донных (Во Время чтения) некоторых инструкцийi-1 -1 о D15 d14 !d13 d12 ] d11 D10 Рис. 7.10. Временные диаграммы работы микросхемы ST93C56C Ha первом шаге генерируется начальное условие, которое заставляет ПЗУ реагировать на поступающие команды. Оно предусматривает подачу высокого уровня на вход выбора микросхемы, стартового бита на вход данных и положительного фронта на тактовый вход микросхемы. Затем следует двухбитовый код, который определяет выполняемую операцию. На следующем шаге в микросхему передаются биты адреса и на последнем - данные. Загрузка битов происходит по положительному фронту тактового импульса. Биты адреса заносятся в микросхему, начиная со старшего (шаг 3). На шаге 4 выполняются только операции чтения и записи данных. Биты данных (сначала старший бит) записываются или считы-ваются по положительному фронту тактового импульса. Набор команд приведен в табл. 7.1. Таблица 7.1. Команды управления операциями чтения/записи

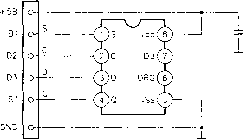

Микросхема ST93C56C соединена с экспериментальной платой параллельного порта, как показано на рис. 7.11. Контакты Dl, D2 и D3 подключены к S, С и D, контакт S1 - к Q. Организация памяти - 128 слов по 16 разрядов (вывод ORG не подключен). Текст программы управления на языке ТР6 приведен ниже.  Контакты на экспериментальной плоте пороллельного порта 0,1мкФ Рис. 7.11. Схема подключения микросхемы ST93C56C к экспериментальной плате параллельного порта Текст программы 9356.PAS Program EEPR0M 93C56 d rive г; («Программа управления FEPR0M, организация памяти 128x16.*) («Соединение с экспериментальной платой параллельного порта: S - выбор микросхемы D2, С - такты 01, D - вход данных D3, О - выход данных S1. *) uses crt, dos, {$1 с \ioexp\TPLIB1 pas) var command.byte, D:array[1..130] of byte; procedure Init, («На все входы управления подан низкий уровень *) begin write data po rt(P add ress,0+0+0), end; Procedure load data(data:byte); (♦Процедура загрузки данных, Select=1, Data=nocTOflHHbie, С1оск=переход 0-1 *) begin write data port(P address,0+2+4*data);(*Select и Data=1.*) delay(1); wnte data port(P address, 1+2+4*data);(*С1оск переходит из 0 в 1 для загрузки данных.*) delay(1), write data port(P address,0+2);(*Select=1, Clock=Data=0. *) delay(1); end; Procedure Start; (•Генерация условия начала. Select=1, Data=1, С1оск=переход 0-1.*) begin write data port(P address,0+0+0); delay(1), (.Select, Clock и Data=0.*) write data port(P address,0+2+4), delay(1); (*Select, Data=1; Clock=0 •) write data port(P address,1+2+4), delay(l), (*Bce входы равны 1.*) write data port(P address,0+2+0); delay(l), (*Select=1; Data и Clock=0.*) end, Procedure Erase(enable flag-boolean); (•Команды разрешения и запрета стирания.*) var l•byte, begin Start;(*Генерация условия начала *) load data(0);(«Загрузка первого бита кода операции 0.*) load data(0);(«Загрузка второго бита кода операции 0 *) if enable flag then («Загрузка 1 и 1 - команда разрешения стирания *) begin load data(1); load data(1); end else («Загрузка 0 и 0 - команда запрета стирания.*) begin load data(1); load data(1); end; for i:=1 to 6 do load data(0), («Загрузка шести холостых бит адреса.*) delay(1); write data port(P address,0); («Все входы=0 для блокирования команды *) delay(10)f 0 ... 85 86 87 88 89 90 91 ... 105 |