Раздел: Документация

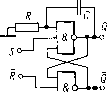

0 ... 65 66 67 68 69 70 71 ... 82 Условное обозначение JK-триггера показано на рис. 12-3, б. Для построения JK-триггера может быть использован тактируемый фронтом D-триггер (рис. 12-3, в). Здесь получаем соотношение D = JQ + KQ, которое обеспечивает функционирование структуры в целом как JK-триггера. Принцип построения универсального JK-триггера, который может работать как в тактируемом, так и в нетактируемом режиме, иллюстрирует рис. 12-3, г. В данном случае устройство содержит тактируемый JK-триггер и ячейку И—ИЛИ. Если приписать обозначениям входов универсального триггера индексы «у», то для схемы рис. 12-3, г можем записать С = = Cy(JyQ + KyQ) ■ Отсюда видим, что при тактированной работе соответствующий фронт на входе С тактируемого JK-триггера будет совпадать с таким же фронтом на входе Су. Если же установить Су=1, то фронты, опрокидывающие триггер, будут определяться перепадами на входах /у и Ку- При этом нетрудно убедиться, что опрокидывание триггера будет производиться в соответствии с правилами работы JK-триггера. Универсальные JK-триггеры весьма удобны для построения различных логических узлов — как с синхронной, так и с асинхронной передачей информации. Примером подобного триггера является ИС типа К155ТВ1, схема которой показана на рис. 12-3, д. Практические схемы триггеров обычно содержат различные вспомогательные входы. В частности, тактируемые триггеры, как правило, имеют также нетактируемые установочные входы S я R (входы S и R у триггера К155ТВ1 —рис. 12-3, д). Для того чтобы облегчить построение логических цепей, в триггерах предусматривают несколько одноименных входов. Так, например, триггер К155ТВ1 имеет объединенные посредством ячеек И три входа / и три входа К, так что / = /1/2/3 и /С = = КхК2Кз (рис. 12-3, д). 12-3. Помехозащитные триггеры Ранее мы говорили, что чем выше быстродействие ИС, тем чувствительнее она к импульсным помехам Поэтому иногда специально принимают меры к снижению быстродействия логической цепи, с тем чтобы повысить ее помехоустойчивость Возможным методом снижения быстродействия интегральных схем типа ТТЛ является соединение одного из входов инвертора с его выходом через конденсатор и с землей через резистор Применяя подобные инверторы в триг-герных структурах, оказывается возможным существенно уменьшить их чувствительность к помехам Схема элементарного SR-триггера, построенного таким способом, показана на рис 12-4 Сопротивление R резисторов должно быть достаточно большим, чтобы присоединение входа к земле через это сопротивление не воспринималось схемой как подача сигнала «нуль». Для ИС серии К155, например, это сопротивление целесообразно устанавливать в диапазоне 5,6—56 кОм В этом случае инвертор ведет себя так, как если бы на этот вход был подан сигнал «единица» При переходе инвертора из состояния «нуль» в состояние «единица» положительный перепад выходного сигнала передается через конденсатор на его вход Это не мешает срабатыванию инвертора. Если же инвертор переходит из единицы в нуль, то отрицательный перепад с выхода, пройдя через конденсатор обратной связи, будет открывать входной многоэмиттерный транзистор и препятствовать тем самым установлению нулевого потенциала на выходе. Схема ведет себя при этом как интегратор, построенный на основе инвертирующего усилителя с емкостной обратной связью Поэтому выходное напряжение подобного инвертора при переходе из единицы в нуль изменяется во времени по закону, близкому к линейному Тем самым снижается быстродействие логического инвертора и повышается его помехоустойчивость. \ Если в триггере по схеме рис. 12-4 принять С— I R \с = мк< и R = fi кОм, то триггер будет срабатывать -1— лишь при длительтсти входных установочных импульсов, превышающей 0,1—0,2 с. Интересным свойством этого триггера является его устойчивость к кратковременным провалам напряжения питания. При выключении питания на время вплоть до нескольких секунд триггер «помнит» свое состояние и при последующем включении питания устанавливается в первоначальное состояние. Такое относительно большое время хранения информации объясняется тем, что при выключении питания закрываются транзисторы выходного каскада инвертора и конденсатор медленно разряжается через запертый я-переход Некоторую информацию о подобных помехозащищенных триггерах можно найти в [61]  Рис 12-4 Низкочастотный триггер с повышенной помехоустойчивостью Глава тринадцатая Регистры и кольцевые счетчики 13-1. Регистры памяти Регистры памяти применяются для хранения информации, представленной в виде двоичного кода. Такие регистры должны по тактовому разрешающему сигналу принимать параллельный код входной информации и хранить его до прихода следующего тактового импульса. Для построения регистров памяти наиболее удобны D-триг-геры. На рис. 13-1 показана схема четырехразрядного регистра памяти К155ТМ5. Он содержит четыре тактируемых потенциалом D-триггера. Если на тактовые входы триггеров подан потенциал С=1, то информация со входов D\—D4 устанавливает триггеры 77— 77 в соответствующие состояния. При С = 0 триггеры хранят запомненную информацию вне зависимости от того, какие потенциалы присутствуют при этом на входах D{—7)4. Регистры памяти могут быть выполнены и на триггерах других типов, например на SR- и JK-триггерах. Однако при этом нужно дополнять каждый триггер инвертором, обеспечивающим подачу на вход R (или К) сигнала, инверсного по отношению к сигналу на входе 5 (или /). Таким способом мы из SR- и JK-триггеров получали бы D-триггеры, которые затем применяли бы так, как показано на рис. 13-1. Если подлежащая хранению информация представлена и прямыми, и инверсными значениями сигнала, то упомянутые выше инверторы, естественно, оказываются лишними. Тактируемые фронтом триггеры могут также использоваться в регистрах памяти. При этом обновление запоминаемой информации будет происходить только в моменты существования соответствующего перепада на тактовом входе. Регистры памяти представляют собой простейшие оперативные запоминающие устройства (ОЗУ). В настоящее время раз- С о— 12

QlQtt 21 S, о 2 Т 3 т 4- Ас-5 Рис 13-1 Регистр памяти К155ТМ5 работаны различные типы интегральных ОЗУ довольно большой емкости. Запись информации в определенную ячейку таких ОЗУ и считывание этой информации производится при наборе на адресных входах ОЗУ кода адреса данной ячейки. 13-2. Регистры сдвига Регистры сдвига широко применяются в цифровой вычислительной технике, и в частности для преобразования последовательного кода в параллельный или параллельного в последовательный. Появление импульса на тактовом входе регистра сдвига вызывает перемещение записанной в нем информации на один разряд вправо или влево. Для построения регистра сдвига удобно применять D-триггеры. На рис. 13-2, а показан регистр сдвига на тактируемых фронтом D-триггерах. Выход Q предыдущего разряда присоединяется ко входу D последующего. Благодаря этому каждый тактовый импульс устанавливает последующий триггер в состояние, в котором до этого находился предыдущий, осуществляя тем самым сдвиг информации на разряд вправо. Вход D первого разряда служит для приема в регистр информации в виде последовательного кода. С каждым тактовым импульсом на этот вход должен подаваться код нового разряда входной информации. Запись параллельного кода информации может быть произведена через нетактируемые установочные 0 ... 65 66 67 68 69 70 71 ... 82 |