Раздел: Документация

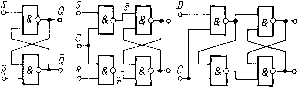

0 ... 64 65 66 67 68 69 70 ... 82 12-2. Принципы построения интегральных триггеров Простейшие нетактируемые SR-триггеры представляют собой две цепи НЕ—И или НЕ—ИЛИ, замкнутые в кольцо. Если отсутствуют внешние воздействия, то на выходе одной ячейки в кольце устанавливается потенциал, равный единице, а на выходе другой — нулю. Подобный триггер, выполненный на ячейках НЕ—И, и его условные обозначения показаны на рис. 12-1, а и б. Опрокидывание этого триггера производится потенциалом «нуль», прикладываемым ко входам S или R, по- а)в)д)  5)г) Рис. 12-1. Схемы (а, в, д) и обозначение (б, г, е) простейших триггеров этому на условном обозначении рис. 12-1, б эти входы помечены кружками. Триггеры, тактируемые импульсом. Простейшие триггеры в тех или иных сочетаниях входят во все типы более сложных триггеров. В частности, тактируемые импульсом триггеры состоят обычно из простейшего триггера и входной логической цепи. В качестве примера на рис. 12-1, в и д показаны схемы SR- и D-триггеров, тактируемых импульсом. Как видно из рис. 12-1, в, для построения тактируемого SR-триггера в данном случае потребовалось добавить к простейшему триггеру две входные ячейки НЕ—И. Если обозначить буквами s я г устанавливающие сигналы простейшего триггера, входящего в эту цепь, то для функций, реализуемых входными ячейками, можно записать следующие выражения: s = SC, r = RC, откуда получаем s = SC и r = RC. Таким образом, если С = 0, то устанавливающие сигналы s я г также равны нулю. И только при наличии разрешающего потенциала С—\ на тактовом входе сигналы, прикладываемые ко входам S я R, могут изменить состояние триггера. D-триггер, показанный на рис. 12-1, д, точно так же устанавливается в состояние, соответствующее сигналу на входе D, только тогда, когда С=1. Условные обозначения триггеров по схемам рис. 12-1, в и д приведены на рис. 12-1, г и е. Триггеры, тактируемые фронтом, могут быть построены по-разному. Один из широко применяемых при этом приемов — это построение двухступенчатого триггера на основе двух триггеров, тактируемых импульсом. Реализованная таким путем схема тактируемого фронтом D-триггера показана на рис. 12-2, а. Как видим, здесь управляющий вход D2 D-триггера второй ступени соединен с прямым выходом Qi триггера первой сту- С

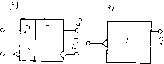

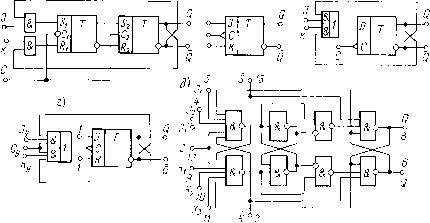

Рис. 12-2. Принцип построения (а) к обозначения (бив) триггеров, тактируемых фронтом пени. Тактовый сигнал подается одновременно на обе ступени, но в триггере второй ступени тактовый вход — инверсный. Благодаря этому при любом сигнале на тактовом входе (С = 0 или С=1) один из двух составляющих триггеров не реагирует на сигнал, поступающий на его управляющий вход. Вследствие этого как при С = 0, так и при С=1 изменение сигнала на входе D не приведет к непосредственному изменению выходного сигнала Q двухступенчатого триггера. И только в тот момент, когда потенциал С переходит из 1 в 0, возможно изменение выходного сигнала Q. Действительно, при С=1 триггер первой ступени воспринимает информацию со входа D. Когда же С становится равным нулю, триггер второй ступени устанавливается в состояние, соответствующее выходному сигналу триггера первой ступени. В иностранной литературе синхронизируемые фронтом триггеры, составленные из двух последовательно включенных триггеров, синхронизируемых импульсами, часто называют триггерами по схеме «хозяин — раб» (master-—slave), имея при этом в виду подчиненность второго триггера первому. Условное обозначение тактируемого фронтом 1/0 D-триггера показано на рис. 12-2, б. Если вход D такого триггера соединить с его же инверсным выходом (D = Q), то каждый перепад 1/0 на его тактовом входе будет приводить к переходу триггера в противополож- ное состояние. Когда, например, триггер устанавливается в со стояние Qn=l, то на его входе D появляется сигнал Dn = Qn = = 0. Поэтому очередной тактовый импульс переводит триггер в новое состояние Qn+I = Dn = 0 и т. д. Таким образом мы на основе D-триггера построили нетактируемый Т-триггер. Условное обозначение подобного Т-триггера показано на рис. 12-2, в. JK-триггер также может быть выполнен по двухступенчатой структуре, если установить соответствующие логические цепи на входе триггера первой ступени (рис. 12-3, а). В дан- а)5)в)  Рис 12-3 Принципы построения (а, в, г, д) и обозначение (6) К-триггеров ном случае St = JQ и Ri = KQ. Если /=1 и К = 0, то при Q = 0 получим Si = l и после окончания первого тактового импульса триггер установится в единицу (Q = l). При /=1, К=0 и Q=l оба входных сигнала триггера первой ступени Si и Ri будут равны нулю и соответственно весь двухступенчатый триггер не будет изменять своего состояния при приходе тактовых импульсов. Таким образом, сигнал «единица» на входе / (при К=0) устанавливает триггер в единицу, если тот был в нуле, или не изменяет состояния триггера, если он уже находится в единице. Подобным же образом по отношению к состоянию Q = 0 действует сигнал «единица» на входе К при / = 0. Если же / = /(=1, то получим Si=l, Ri = 0 при Q = 0 или Si = 0, Ri = l при Q = l. Вследствие этого наличие единицы на обоих управляющих входах триггера (/ и К) приведет к переходу триггера в противоположное состояние при наличии соответствующего фронта сигнала на тактовом входе. 0 ... 64 65 66 67 68 69 70 ... 82 |