Раздел: Документация

0 1 2 3 4 5 6 7 ... 30 F1

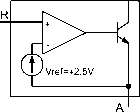

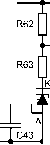

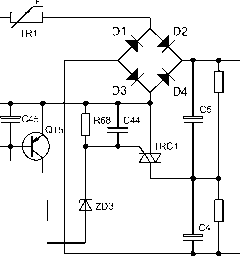

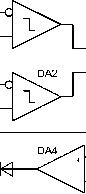

LT C40 D40 IC3-TL431 Кi  D41 y C3 C2 D42 R60 C42 R69 .X- JL R61 C41 R64 -czb- 1 1R65  IC3  R70 Рис. 10. Схема автоматического распознавания номинала сетевого напряжения ИБП SP-200W. вого напряжения через D41 протекает ток зарядки конденсатора С41 по цепи: 0-й провод сети - С41 -D41 - С40 - фазный провод сети. В положительные полупериоды сетевого напряжения конденсатор С40 отдает накопленную энергию обратно в сеть через рекуперационный (возвратный) диод D40. Напряжением с конденсатора С41 как и ранее запитывается бистабиль-ная схема на транзисторах Q15, Q16. Управление состоянием бистабильной схемы производится с помощью специальной микросхемы ЮЗ, которую для простоты можно назвать управляемым стабилитроном. Принцип действия такого стабилитрона заключается в том, что его напряжение стабилизации не является постоянной величиной, а зависит от потенциала на управляющем электроде R. Такая ИМС выпускается рядом зарубежных фирм. Например, фирма Texas Instruments (США) выпускает ИМС TL431C в пластмассовом трехвы-водном корпусе. По внешнему виду микросхема напоминает обычный маломощный транзистор (корпус ТО-92). Функцию механического переключателя 110/220В выполняет, как и ранее, симистор TRC1. Датчиком номинала сетевого напряжения является уровень напряжения на конденсаторе С42, который заряжается в положительные полупериоды сетевого напряжения через диод D42 по цепи: фазовый провод сети - D42 - R60 - С42 - 0-й провод сети. Резистор R60 образует с конденсатором С42 делитель и большая часть сетевого напряжения падает именно на этом резисторе. При этом напряжение на конденсаторе С42 получается включено согласно с напряжением на конденсаторе С41. Суммарное напряжение с этих двух конденсаторов подается на резистивный делитель R61, R64R65. Поэтому через этот делитель протекает ток разряда этого суммарного источника по цепи: (+)С42 -R61 - R64\\R65 - R67 - (-)С41. Падение напряжения с нижнего плеча делителя R64, R65 подается на управляющий электрод микросхемы ЮЗ. При подключении к сети 110В конденсатор С42 заряжен до некоторого невысокого уровня. Поэтому напряжение на управляющем Электроде микросхемы ЮЗ невелико (не превышает уровень 2,5В). Состояние микросхемы эквивалентно разомкнутому состоянию ключа (стабилитрон закрыт). Поэтому транзисторы Q15, Q16 бистабильной схемы закрыты. Все напряжение с конденсатора С41 оказывается приложенным через резисторы R68, R67 к стабилитрону ZD3, который "пробивается", и поэтому в управляющий электрод симистора течет открывающий его ток по цепи: (+)С41 - управляющий переход TRC1 - ZD3 -R67 - (-)С41. Симистор TRC1 открывается и подключает 0-й провод сети к средней точке емкостной стойки силового полумоста, что эквивалентно замкнутому состоянию механического переключателя 110/220В. При подключении к сети 220В напряжение на конденсаторе С42, а значит, и на управляющем электроде микросхемы ЮЗ возрастает вдвое и превышает +2.5В. Поэтому, стабилитрон "пробивается". Это приводит к приоткрыванию транзистора Q15 бистабильной схемы, т.к. базовый делитель R62, R63 этого транзистора подключается к "общему проводу" через внутреннее сопротивление микросхемы ЮЗ, и через управляющий переход Q15 протекает ток. Так как транзисторы бистабильной схемы охвачены положительной обратной связью, то приоткрывание Q15 вызывает лавинообразный процесс взаимного открывания обоих транзисторов и переход их в состояние насыщения. В результате стабилитрон ZD3 и управляющий переход симистора TRC1 оказываются зашунтированы малым внутренним сопротивлением открытых транзисторов бистабильной схемы. Поэтому стабилитрон ZD3 и симистор TRC1 остаются в закрытом состоянии, что эквивалентно разомкнутому состоянию механического переключателя 110/220В. Итак: первым обязательным условием работы БП является выработка постоянного напряжения +310В. Вторым обязательным условием нормальной работы ИБП является работа схемы пуска, которая позволяет запустить переключающую схему управления. УПРАВЛЯЮЩАЯ МИКРОСХЕМА В современных ИБП для формирования управляющего напряжения переключения мощных транзисторов преобразователя обычно используются специализированные интегральные микросхемы (ИМС). Идеальная управляющая ИМС для обеспечения нормальной работы ИБП в режиме ШИМ должна удовлетворять большинству из перечисленных ниже условий: •рабочее напряжение не выше 40В; •наличие высокостабильного термостабилизи-рованного источника опорного напряжения; •наличие генератора пилообразного напряже- •обеспечение возможности синхронизации внешним сигналом программируемого плавного запуска; •наличие усилителя сигнала рассогласования с высоким синфазным напряжением; •наличие ШИМ-компаратора; •наличие импульсного управляемого триггера; •наличие двухканального предоконечного каскада с защитой от КЗ; •наличие логики подавления двойного импульса; •наличие средств коррекции симметрии выходных напряжений; •наличие токоограничения в широком диапазоне синфазных напряжений, а также токоограничения в каждом периоде с отключением в аварийном режиме; •наличие автоматического управления с прямой передачей; •обеспечение отключения при понижении напряжения питания; •обеспечение защиты от перенапряжений; •обеспечение совместимости с ТТЛ/КМОП логикой; •обеспечение дистанционного включения и отключения. В качестве схемы управления для рассматриваемого класса ИБП в подавляющем большинстве случаев используется микросхема типа Усилитель / ПРЯМ0Й ВХ°Д С ОШИбкИ 1 \,- \ инверсный вход 2. обратная связь [Т регулировка мертвой зоны ГТ Сг ГТ Rr [Т "общий" ГТ коллектор 1 [jL и 16J прямой вход \усилитель Щ инверсный вход/ошибки 2 ТП Uref=+5B ТЛ режим ТЛ +11пит ТП коллектор 2 То"1 эмиттер 2 "эП эмиттер 1 Рис. 11. Управляющая микросхема TL494 и ее цоколевка. TL494CN, выпускаемая фирмой TEXAS INSTRUMENT (США) (рис.11). Она реализует большинство из перечисленных выше функций и выпускается рядом зарубежных фирм под разными наименованиями. Например, фирма SHARP (Япония) выпускает микросхему IR3M02, фирма FAIRCHILD (США) - иА494, фирма SAMSUNG (Корея) - КА7500, фирма FUJITSU (Япония) -МВ3759 и т.д. Все эти микросхемы являются полными аналогами отечественной микросхемы КР1114ЕУ4. Рассмотрим подробно устройство и работу этой управляющей микросхемы. Она специально разработана для управления силовой частью ИБП и содержит в своем составе (рис.12): •генератор пилообразного напряжения DA6; частота ГПН определяется номиналами резистора и конденсатора, подключенных к 5-му и 6-му выводам, и в рассматриваемом классе БП выбирается равной примерно 60 кГц; •источник опорного стабилизированного напряжения DA5 (Uref=+5,0B) с внешним выходом (вывод 14); •компаратор "мертвой зоны" DA1; •компаратор ШИМ DA2; •усилитель ошибки по напряжению DA3; •усилитель ошибки по сигналу ограничения тока DA4; •два выходных транзистора VT1 и VT2 с открытыми коллекторами и эмиттерами; +11ПИТ Rt Ct ■ АЛЛ osc DA6 DD2 DA1 DA7 0.12V 0.7V DA3 ■f>b  L-IdTTq DD1 С Q<fr DD7 DA8 0.7mA ■е- 15 12 & & DD3 DD5 DD4 1 VT1 К" DD6 VT2 DA5 Reference regulator 16 Общий Uref=+5B 9 11 10 13 Рис.12. Функциональная схема ИМС TL494. •динамический двухтактный D-триггер в режиме деления частоты на 2 - DD2; •вспомогательные логические элементы DD1 (2-ИЛИ), DD3 (2-И), DD4 (2-И), DD5 (2-ИЛИ-НЕ), DD6 (2-ИЛИ-НЕ), DD7 (НЕ); •источник постоянного напряжения с номиналом 0,1В DA7; •источник постоянного тока с номиналом 0,7мА DA8. Схема управления будет запускаться, т.е. на 8 и 11 выводах появятся последовательности импульсов в том случае, если на вывод 12 подать любое питающее напряжение, уровень которого находится в диапазоне от +7 до +40 В. Всю совокупность функциональных узлов, входящих в состав ИМС TL494, можно условно разбить на цифровую и аналоговую часть (цифровой и аналоговый тракты прохождения сигналов). К аналоговой части относятся усилители ошибок DA3, DA4, компараторы DA1, DA2, генератор пилообразного напряжения DA6, а также вспомогательные источники DA5, DA7, DA8. Все остальные элементы, в том числе и выходные транзисторы, образуют цифровую часть (цифровой тракт). Рассмотрим в начале работу цифрового тракта. Временные диаграммы, поясняющие работу микросхемы, приведены на рис. 13. Из временных диаграмм видно, что моменты появления выходных управляющих импульсов микросхемы, а также их длительность (диаграммы 12 и 13) определяются состоянием выхода логического элемента DD1 (диаграмма 5). Остальная "логика" выполняет лишь вспомогательную функцию разделения выходных импульсов DD1 на два канала. При этом длительность выходных импульсов микросхемы определяется длительностью открытого состояния ее выходных транзисторов VT1, VT2. Так как оба эти транзистора имеют открытые коллекторы и эмиттеры, то возможно двоякое их подключение. При включении по схеме с общим эмиттером выходные импульсы снимаются с внешних коллекторных нагрузок транзисторов (с выводов 8 и 11 микросхемы), а сами импульсы направлены выбросами вниз от положительного уровня (передние фронты импульсов отрицательны). Эмиттеры транзисторов (выводы 9 и 10 микросхемы) в этом случае, как правило, заземляются. При включении по схеме с общим коллектором внешние нагрузки подключаются к эмиттерам транзисторов и выходные импульсы, направленные в этом случае выбросами вверх (передние фронты импульсов положительны), снимаются с эмиттеров транзисторов VT1, VT2. Коллекторы этих транзисторов подключаются к шине питания управляющей микросхемы (Upom). Выходные импульсы остальных функциональных узлов, входящих в состав цифровой части микросхемы TL494, направлены выбросами вверх, независимо от схемы включения микросхемы. Триггер DD2 является двухтактным динамическим D-триггером. Принцип его работы заключается в следующем. По переднему (положительному) фронту выходного импульса элемента DD1 состояние входа D триггера DD2 записывается во внутренний регистр. Физически это означает, что переключается первый из двух триггеров, входя- щих в состав DD2. Когда импульс на выходе элемента DD1 заканчивается, то по заднему (отрицательному) фронту этого импульса переключается второй триггер в составе DD2, и состояние выходов DD2 меняется (на выходе Q появляется информация, считанная со входа D). Это исключает возможность появления отпирающего импульса на базе каждого из транзисторов VT1, VT2 дважды в течение одного периода. Действительно, пока уровень импульса на входе С триггера DD2 не изменился, состояние его выходов не изменится. Поэтому импульс передается на выход микросхемы по одному из каналов, например верхнему (DD3, DD5, VT1). Когда импульс на входе С заканчивается, триггер DD2 переключается, запирает верхний и отпирает нижний канал (DD4, DD6, VT2). Поэтому следующий импульс, поступающий на вход С и входы DD5, DD6 будет передаваться на выход микросхемы по нижнему каналу. Таким образом каждый из выходных импульсов элемента DD1 своим отрицательным фронтом переключает триггер DD2 и этим меняет канал прохождения следующего импульса. Поэтому в справочном материале на управляющую микросхему указывается, что архитектура микросхемы обеспечивает подавление двойного импульса, т.е. исключает появление двух отпирающих импульсов на базе одного и того же транзистора за период. Рассмотрим подробно один период работы цифрового тракта микросхемы. Появление отпирающего импульса на базе выходного транзистора верхнего (VT1) либо нижнего (VT2) канала определяется логикой работы элементов DD5, DD6 ("2ИЛИ-НЕ") и состоянием элементов DD3, DD4 ("2-И"), которое, в свою очередь, определяется состоянием триггера DD2. Логика работы элемента 2-ИЛИ-НЕ, как известно, заключается в том, что на выходе такого элемента появляется напряжение высокого уровня (логическая 1) в том лишь единственном случае, если на обоих его входах присутствуют низкие уровни напряжений (логические 0). При остальных возможных комбинациях входных сигналов на выходе элемента 2 ИЛИ-НЕ присутствует низкий уровень напряжения (логический 0). Поэтому если на выходе Q триггера DD2 присутствует логическая 1 (момент t-i диаграммы 5 рис.13), а на выходе /Q - логический 0, то на обоих входах элемента DD3 (2И) окажутся логические 1 и, следовательно, логическая 1 появится на выходе DD3, а значит и на одном из входов элемента DD5 (2ИЛИ-НЕ) верхнего канала. Следовательно, независимо от уровня сигнала, поступающего на второй вход этого элемента с выхода элемента DD1, состоянием выхода DD5 будет логический 0, и транзистор VT1 останется в закрытом состоянии. Состоянием же выхода элемента DD4 будет логический 0, т.к. логический 0 присутствует на одном из входов DD4, поступая туда с выхода /Q триггера DD2. Логический 0 с выхода элемента DD4 поступает на один из входов элемента DD6 и обеспечивает возможность прохождения импульса через нижний канал. Этот импульс положительной полярности (логическая 1) появится на выходе DD6, а значит и на базе VT2 на время паузы между выходными импульсами элемента 0 1 2 3 4 5 6 7 ... 30

|