Раздел: Документация

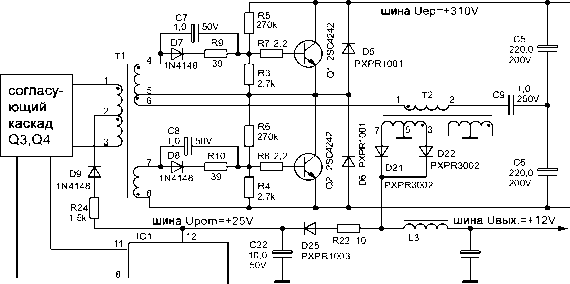

0 ... 2 3 4 5 6 7 8 ... 30 DD1 (т.е. на время, когда на выходе DD1 присутствует логический 0 - интервал trt2 диаграммы 5 рис.13). Поэтому транзисгор VT2 открывается и на его коллекторе появляется импульс выбросом вниз от положительного уровня (в случае включения по схеме с общим эмиттером). Начало следующего выходного импульса элемента DD1 (момент t2 диаграммы 5 рис.13) не изменит состояния элементов цифрового тракта микросхемы, за исключением элемента DD6, на выходе которого появится логический 0, и поэтому транзистор VT2 закроется. Завершение выходного импульса DD1 (момент t3) обусловит изменение состояния выходов триггера DD2 на противоположное (логический 0 - на выходе Q, логическая 1 - на выходе /Q). Поэтому поменяется состояние выходов элементов DD3, DD4 (на выходе DD3 - логический 0, на выходе DD4 - логическая 1). Начавшаяся в момент t3 пауза на выходе элемента DD1 обусловит возможность открывания транзистора VT1 верхнего канала. Логический 0 на выходе элемента DD3 "подтвердит" эту возможность, превращая ее в реальное появление отпирающего импульса на базе транзистора VT1. Этот импульс длится до момента и, после чего VT1 закрывается, и процессы повторяются. Таким образом основная идея работы цифрового тракта микросхемы заключается в том, что длительность выходного импульса на выводах 8 и 11 (либо на выводах 9 и 10) определяется длительностью паузы между выходными импульсами элемента DD1. Элементы DD3, DD4 определяют канал прохождения импульса по сигналу низкого уровня, появление которого чередуется на выходах Q и /О. триггера DD2, управляемого тем же элементом DD1. Элементы DD5, DD6 представляют собой схемы совпадения по низкому уровню. Для полноты описания функциональных возможностей микросхемы следует отметить еще одну важную ее особенность. Как видно из функциональной схемы рисунке входы элементов DD3, DD4 объединены и выведены на вывод 13 микросхемы. Поэтому если на вывод 13 подана логическая 1, то элементы DD3, DD4 будут работать как повторители информации с выходов Q и /О. триггера DD2. При этом элементы DD5, DD6 и транзисторы VT1, VT2 будут переключаться со сдвигом по фазе на половину периода, обеспечивая работу силовой части ИБП, построенной по двухтактной полумостовой схеме. Если на вывод 13 будет подан логический 0, то элементы DD3, DD4 будут заблокированы, т.е. состояние выходов этих элементов не будет изменяться (постоянный логический 0). Поэтому выходные импульсы элемента DD1 будут воздействовать на элементы DD5, DD6 одинаково. Элементы DD5, DD6, а значит и выходные транзисторы VT1, VT2, будут переключаться без сдвига по фазе (одновременно). Такой режим работы управляющей микросхемы используется в случае, если силовая часть ИБП выполнена по однотактной схеме. Коллекторы и эмиттеры обоих выходных транзисторов микросхемы в этом случае объединяются с целью умощнения. В качестве "жесткой" логической единицы в двухтактных схемах используется выходное напряжение внутреннего источника микросхемы Uref (вывод 13 микросхемы объединяется с выводом 14). Теперь рассмотрим работу аналогового тракта микросхемы. Состояние выхода DD1 определяется выходным сигналом компаратора ШИМ DA2 (диаграмма 4), поступающим на один из входов DD1. Выходной сигнал компаратора DA1 (диаграмма 2), поступающий на второй вход DD1, не влияет в нормальном режиме работы на состояние выхода DD1, которое определяется более широкими выходными импульсами ШИМ - компаратора DA2. Кроме того, из диаграмм рис.13 видно, что при изменениях уровня напряжения на неинвертиру-ющем входе ШИМ компаратора (диаграмма 3) ширина выходных импульсов микросхемы (диаграммы 12, 13) будет пропорционально изменяться. В нормальном режиме работы уровень напряжения на неинвертирующем входе компаратора ШИМ DA2 определяется только выходным напряжением усилителя ошибки DA3 (т.к. оно превышает выходное напряжение усилителя DA4), которое зависит от уровня сигнала обратной связи на его неинвертирующем входе (вывод 1 микросхемы). Поэтому при подаче сигнала обратной связи на вывод 1 микросхемы ширина выходных управляющих импульсов будет изменяться пропорционально изменению уровня этого сигнала обратной связи, который, в свою очередь, изменяется пропорционально изменениям уровня выходного напряжения ИБП, т.к. обратная связь заводится именно оттуда. Промежутки времени между выходными импульсами на выводах 8 и 11 микросхемы, когда оба выходных транзистора VT1 и VT2 ее закрыты, называются "мертвыми зонами". Компаратор DA1 называется компаратором "мертвой зоны", т.к. он определяет минимально возможную ее длительность. Поясним это подробнее. Из временных диаграмм рис.13 следует, что если ширина выходных импульсов ШИМ-компа-ратора DA2 будет в силу каких-либо причин уменьшаться, то начиная с некоторой ширины этих импульсов выходные импульсы компаратора DA1 станут шире выходных импульсов ШИМ-компаратора DA2 и начнут определять состояние выхода логического элемента DD1, а значит и. ширину выходных импульсов микросхемы. Другими словами, компаратор DA1 ограничивает ширину выходных импульсов микросхемы на некотором максимальном уровне. Уровень ограничения определяется потенциалом на неинвенти-рующем входе компаратора DA1 (вывод 4 микросхемы) в установившемся режиме. Однако, с другой стороны, потенциал на выводе 4 будет определять диапазон широтной регулировки выходных импульсов микросхемы. При увеличении потенциала на выводе 4 этот диапазон сужается. Самый широкий диапазон регулировки получается тогда, когда потенциал на выводе 4 равен 0. Однако в этом случае появляется опасность, связанная с тем, что ширина "мертвой зоны" может стать равной 0 (например, в случае значительного возрастания потребляемого от ИБП тока). Это означает, что управляющие импульсы на выводах 8 и 11 микросхемы будут следовать непосредственно друг за другом. Поэтому может возникнуть ситуация, известная под названием "пробой по стойке". Она объясняется инерционностью силовых транзисторов инвертора, которые не могут открываться и закрываться мгновенно. Поэтому, если одновременно на базу открытого до этого транзистора подать запирающий сигнал, а на базу закрытого транзистора - отпирающий (т.е. с нулевой "мертвой зоной"), то получится ситуация, когда один транзистор еще не закрылся, а другой уже открыт. Тогда и возникает пробой по транзисторной стойке полумоста, который заключается в протекании сквозного тока через оба транзистора. Ток этот, как видно из схемы рис. 5, минует первичную обмотку силового трансформатора и практически ничем не ограничен. Защита по току в этом случае не работает, т.к. ток не протекает через токовый датчик (на схеме не показан; конструкция и принцип действия применяемых токовых датчиков будут подробно рассмотрены в последующих разделах), а значит, этот датчик не может выдать сигнал на схему управления. Поэтому сквозной ток достигает очень большой величины за очень короткий промежуток времени. Это приводит к резкому возрастанию выделяющейся на обоих силовых транзисторах мощности и практически мгновенному выходу их из строя (как правило, пробой). Кроме того, броском сквозного тока могут быть выведены из строя диоды силового выпрямительного моста. Процесс этот заканчивается перегоранием сетевого предохранителя, который из-за своей инерционности не успевает защитить элементы схемы, а лишь защищает от перегрузки первичную сеть. Поэтому управляющее напряжение; подаваемое на базы силовых транзисторов должно быть сформировано таким образом, чтобы сначала надежно закрывался бы один из этих транзисторов, а уже потом открывался бы другой. Другими словами, между управляющими импульсами, подаваемыми на базы силовых транзисторов обязательно должен быть временной сдвиг, не равный нулю ("мертвая зона"). Минимальная допустимая длительность "мертвой зоны" определяется инерционностью применяемых в качестве силовых ключей транзисторов. Архитектура микросхемы позволяет регулировать величину минимальной длительности "мертвой зоны" с помощью потенциала на выводе 4 микросхемы. Потенциал этот задается с помощью внешнего делителя, подключаемого к шине выходного напряжения внутреннего опорного источника микросхемы Uref. В некоторых вариантах ИБП такой делитель отсутствует. Это означает, что после завершения процесса плавного пуска (см. ниже) потенциал на выводе 4 микросхемы становится равным 0. В этих случаях минимально возможная длительность "мертвой зоны" все же не станет равной 0, а будет определяться внутренним источником напряжения DA7 (0,1В), который подключен к не-инвертирующему входу компаратора DA1 своим положительным полюсом, и к выводу 4 микросхемы - отрицательным. Таким образом, благодаря включению этого источника ширина выходного  n i н J н i i (=1 i i — . I I—I w и,г Рис. 13. Работа ИМС TL494 в номинальном режиме: U3, U4, U5 - напряжения на выводах 3, 4, 5. импульса компаратора DA1, а значит и ширина "мертвой зоны", ни при каких условиях не может стать равной 0, а значит "пробой по стойке" будет принципиально невозможен. Другими словами, в архитектуру микросхемы заложено ограничение максимальной длительности ее выходного импульса (минимальной длительности "мертвой зоны"). Если имеется делитель, подключенный к выводу 4 микросхемы, то после плавного пуска потенциал этого вывода не равен 0, поэтому ширина выходных импульсов компаратора DA1 определяется не только внутренним источником DA7, но и остаточным (после завершения процесса плавного запуска) потенциалом на выводе 4. Однако при этом, как было сказано выше, сужается динамический диапазон широтной регулировки ШИМ компаратора DA2. СХЕМА ПУСКА Схема пуска предназначена для получения напряжения, которым можно было бы запитать управляющую микросхему с целью ее запуска после включения ИВП в питающую сеть. Поэтому под пуском подразумевается запуск в работу в первую очередь управляющей микросхемы, без нормального функционирования которой невозможна работа силовой части и всей схемы ИБП в целом. Схема пуска может быть построена двумя различными способами: •с самовозбуждением; •с принудительным возбуждением. Схема с самовозбуждением используется, например, в ИБП GT-150W (рис.14). Выпрямленное напряжение сети Uep подается на резистивный делитель R5, R3, R6, R4, являющийся базовым для обоих силовых ключевых транзисторов Q1, Q2. Поэтому через транзисторы под воздействием суммарного напряжения на конденсаторах С5, С6 (Uep) начинает протекать базовый ток по цепи (+)С5 - R5 - R7 - 6-э Q1 - R6 - R8 - б-э Q2 - "общий провод" первичной стороны - (-)С6. Оба транзистора приоткрываются этим током. В результате через участки коллектор-эмиттер обоих транзисторов начинают протекать токи взаимно противоположных направлений по цепям: •через Q1: (+)С5 - шина +310 В - к-э Q1 - 5-6 Т1 -1-2 Т2-С9-(-)С5. •через Q2: (+)С6 - С9 - 2-1 12 - 6-5 Т1 - к-э Q2 -"общий провод"первичной стороны - (-)С6. Если бы оба тока, протекающие через дополнительные (пусковые) витки 5-6 T1 в противоположных направлениях, были бы равны, то результирующий ток был бы равен 0, и схема не смогла бы запуститься. Однако в силу технологического разброса коэффициентов усиления по току транзисторов Q1, Q2 всегда какой-либо один из этих токов больше другого, т.к. транзисторы приоткрыты в разной степени. Поэтому результирующий ток через витки 5-6 T1 не равен 0 и имеет то или иное направление. Допустим, что преобладает ток через транзистор Q1 (то есть Q1 приоткрыт в большей степени, чем Q2) и, следовательно, ток протекает в направлении от вывода 5 к выводу 6 T1. Дальнейшие рассуждения основываются на этом допущении. Однако, справедливости ради нужно отметить, что преобладающим может оказаться и ток через транзистор Q2, и тогда все далее описываемые процессы будут относиться к транзистору Q2. Протекание тока через витки 5-6 T1 вызывает появление ЭДС взаимоиндукции на всех обмотках управляющего трансформатора Т1. При этом (+)ЭДС возникает на выводе 4 относительно вывода бив базу Q1 под воздействием этой ЭДС течет дополнительно приоткрывающий его ток по цепи: 4Т1-D7-R9-R7- б-э Q1 - 5 Т1. Одновременно на выводе 7 Т1 появляется (-) ЭДС относительно вывода 8, т.е. полярность этой ЭДС оказывается запирающей для Q2 и он закрывается. Далее вступает в действие положительная обратная связь (ПОС). Действие ее заключается в том, что при возрастании тока через участок коллектор-эмиттер Q1 и витки 5-6 Т1 на обмотке 4-5 Т1 действует возрастающая ЭДС, которая, создавая дополнительный базовый ток для Q1, еще в большей степени приоткрывает его. Процесс этот развивается лавинообразно  схема управления (TL494CN) Рис. 14. Схема запуска с самовозбуждением ИБП GT-150W. 0 ... 2 3 4 5 6 7 8 ... 30 |