Раздел: Документация

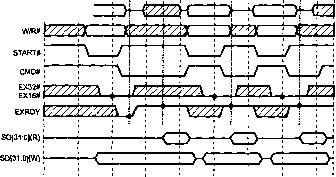

0 ... 42 43 44 45 46 47 48 ... 131 ВСЮ ;[ ; BALEJ y\-j-j-j-j SA[19:0], SBHEi Действительный адрес 1*23:17] ЩШАдрес ШШ)Щ))ШЩПШШШШ\ смо*;V ; \I I SD[15:0] I------I---;---!---(Данные)- \ MEM CS16 I/ I I ! I/O CH RDY I Ч I Г~"> \ Рис. 4.5. Временные диаграммы циклов чтения или записи на шине ISA В каждом из рассматриваемых циклов активными (с низким уровнем) могут быть только сигналы лишь из одной строки данного списка. Цикл прямого доступа к памяти, в котором это правило не соблюдается, рассмотрен в приложении А (см. рис. А.2). По адресоваггяому ему спаду сигнала чтения устройство должно выдать на шину данных содержимое адресуемой ячейки и удерживать его, пока не произойдет подъем сигнала. Во время циклов записи процессор выставляет действительные данные несколько позже начала (спада) сигнала записи. Уст- и MASTER* — запрос от устройства, использующего 16-битный канал DMA на управление шиной. При получении подтверждения DACK [5:7] Bus-Master может захватить шину (не более чем на 15 мкс). Обобщенные временные диаграммы циклов чтения или записи памяти или ввода/вывода приведены на рис. 4.5. Здесь условный сигнал CMD* изображает один из сигналов: »SMEMRD#, MEMRD* — в цикле чтения памяти; шSMEMWR#, MEMWR# — в цикле записи памяти; шIORD# — в цикле чтения порта ввода/вывода; »>IOWR# — в цикле записи порта ввода/вывода. Т11TW1Т21 III I ройство должно фиксировать для себя эти данные в конце цикла по подъему сигнала. Обращение к портам ввода/вы-вода отличается тем, что сигналы LA[32:17] не используются. Минимальная длительность цикла определяется чипсетом и может программироваться опциями BIOS Setup заданием тактов ожидания. При этом циклы обращения к памяти короче циклов обращения к портам ввода/вывода. В шине AT для управления минимальной длительностью цикла используются также сигналы управления разрядностью передачи: если устройство поддерживает 16-битные передачи, предполагается, что оно может работать с меньшим количеством тактов ожидания. Этим объясняется, что в Setup длительности циклов ISA задаются раздельно как для памяти и ввода/вывода, так и для 8- и 16-битных операций. Если устройство не работает с заданными циклами, оно может вводить дополнительные такты ожидания, используя сигнал IOCHRDY, но при этом недопустимо удлинять цикл более чем на 15 мкс. Шина EISA позволяет устройствам работать как в режиме ISA, так и в новых режимах EISA. Из сигналов ISA используются линии адреса/данных с расширением их до 32 бит, сигналы прерываний и прямого доступа к памяти и синхронизации. Для своих циклов обмена EISA использует собственный набор управляющих сигналов с обязательной синхронизацией по сигналу BCLK. Сигналы IORD# и IOWR# при обращении к EISA-портам не используются. Вместо них применяются сигналы обращения М/Ю# и W/R#. В EISA-циклах не используется сигнал SBHE; он заменен сигналами разрешения байт ВЕ[3:0]. Вместо общего сигнала AEN каждый слот имеет собственный сигнал AENx. К сигнала» расширения шины EISA относятся следующие: и 1 А[23:16] — опережающие сигналы адреса, требующие защелкивания по спаду сигнала BALE. * LA[31:24]# — аналогично LA [2:23], но с инверсией. т ВЕ[3:0]# — индикаторы действительности данных в байтах 0-3 при EISA-цикле. » М/Ю# — обращение к памяти (1) или портам (0) EISA. W/R# — запись (1) или чтение (0) EISA. ЕХ16#, ЕХ32# — индикаторы разрядности ресурсов. SLBURST# — адресуемое устройство поддерживает пакетный режим обмена. MSBURST* — уведомление устройства, подавшего сигнал SLBURST, о намерении инициировать пакетный обмен. LOCK* — обеспечение исключительного права доступа активного EISA Bus-Master к памяти или портам. EXRDY — готовность EISA-устройства; аналогично сигналу IOCHRDCY. START* — отмечает начало цикла EISA-доступа. Во время действия этого сигнала фиксируется адрес и определяется тип обращения. CMD* — задает временные параметры цикла; действует после сигнала START*. MREQx* — EISA Bus-Master слота «х» запрашивает управление шиной. МАКх* — EISA Bus-Master слота «х» получает управление шиной от арбитра. BCLK ВЕРЯ]» /УУУУГ  Рис. 4.6. Временные диаграммы одиночных циклов на шине EISA 0 ... 42 43 44 45 46 47 48 ... 131 |