Раздел:

Документация0 ...

114 115 116 117 118 119 120 ...

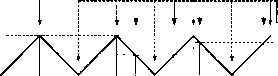

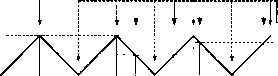

195 Устанавливается флаг прерывания ОСл (ОСлх)

ОСл (ОСлх)

ОСл (ОСлх)

Период

-1-

-2-

Г~1 гт

Обновляется регистр ОСЯл (ОСЯлх)

Устанавливается флаг прерывания ТО\/л

СОМл1:0 = 2 (СОМлх1:0 = 2)

Г* СОМл1:0 = 3 -I (СОМлх1:0 = 3)

л = 0 или 2

Рис. 7.15. Формирование ШИМ-сигнала в режиме Phase Correct PWM

Таблица 7.18. Устойчивые состояния выхода схемы сравнения

СОМл1 (COM/utl) | СОМлО (СОМлхО) | Регистр ОСИл (OCItoA/OCItoB) | Состояние вывода ОСя (ОСлА/ОСлВ) |

1 | 0 | $00 | 0 |

1 | 0 | Максимальное значение | 1 |

1 | 1 | $00 | 1 |

1 | 1 | Максимальное значение | 0 |

Примечание, п = 0 или 2.

Частота генерируемого в рассматриваемом режиме сигнала определяется выражением

г /clk I/Q

JoCn N • 512 где N— коэффициент деления предделителя (см. Табл. 7.12).

7.5.3. Асинхронный режим

В моделях ATmega64x и ATmega 128х в асинхронном режиме может работать таймер/счетчик ТО. В остальных моделях (кроме ATmega8515x) такой возможностью обладает таймер/счетчик Т2.

В асинхронном режиме на вход предделителя поступает сигнал от кварцевого генератора таймера/счетчика, что позволяет использовать таймер/счетчик в качестве часов реального времени. В качестве источника сигнала, как правило, используется кварцевый резонатор, подключаемый к выводам TOSC1 и TOSC2 микроконтроллера. В некоторых моделях можно использовать сигнал от внешней схемы, подаваемый на вывод TOSC1. Тактовый генератор таймера/счетчика оптимизирован для работы на частоте 32 768 Гц, при этом она должна быть как минимум в 4 раза ниже частоты тактового сигнала микроконтроллера.

Непосредственная запись в регистры TCNTh, OCR/j (OCR/jA/OCR/jB) и TCCRai (TCCR/jA/TCCR/jB) в асинхронном режиме синхронизируется с тактовым сигналом таймера/счетчика. При записи числа в любой из указанных регистров оно сохраняется в специальном временном регистре, своем для каждого регистра таймера/счетчика. А пересылка содержимого временного регистра в рабочий регистр таймера/счетчика осуществляется по третьему после записи положительному фронту сигнала на выводе TOSC1. Соответственно, запись нового значения можно производить только после пересылки содержимого временного регистра в регистр таймера/счетчика.

Для определения момента действительного изменения регистров таймера/счетчика, а также для управления асинхронным режимом таймера/счетчика предназначен регистр ASSR. Формат этого регистра приведен на Рис. 7.16, а описание его битов — в Табл. 7.19.

Чтение (R)/3anncb (W) Начальное значение

Чтение (R)/3anncb (W) Начальное значение

Чтение (R)/3anncb (W) Начальное значение

Чтением/Запись (W) Начальное значение

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

- | - | - | - | AS0 | TCN0UB | OCR0UB | TCR0UB |

R | R | R | R | R/W | R | R | R |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

- | - | - | - | AS2 | TCN2UB | 0CR2UB | TCR2UB |

R | R | R | R | R/W | R | R | R |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

- | - | - | EXCLK | AS2 | TCN2UB | 0CR2UB | TCR2UB |

R | R | R | R/W | R/W | R | R | R |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

- | EXCLK | AS2 | TCN2UB | 0CR2AUB | 0CR2BUB | TCR2AUB | TCR2BUB |

R/W R/W О О

АТтеда64х/128х

АТтедаВ535х

АТтедаВх/16х/32х

АТтеда162х

АТтеда165х

АТтеда325х/3250х

АТтеда645х/6450х

АТтеда48х/88х/16Вх АТтеда164х/324х/644х АТтеда640х/1280х/1281х АТтеда2560х/2561х

Рис. 7.16. Формат регистра ASSR

Таблица 7.19. Биты регистра ASSR

Название | Описание |

ASn | Переключение режима работы. Если бит установлен в 1, то на вход предделителя таймера/счетчика Тл поступают импульсы с кварцевого генератора таймера/счетчика (асинхронный режим). В этом режиме выводы TOSC1 и TOSC2 используются для подключения кварцевого резонатора и соответственно не могут использоваться как контакты ввода/вывода общего назначения. Если бит сброшен в 0, то на вход предделителя поступает внутренний тактовый сигнал микроконтроллера. В этом случае выводы TOSC1 и TOSC2 являются линиями ввода/вывода общего назначения. При изменении состояния этого бита содержимое регистров TCNT/i, OCR/j (OCR/?A/OCR/?B) и TCCR/? (TCCR/?A/TCCR/?B) может быть повреждено |

EXCLK | Разрешение внешнего тактового сигнала. При установке бита в 1 включается входной буфер внешнего тактового сигнала и таймер/счетчик может тактироваться внешним сигналом, подаваемым на вход TOSC 1. Установка этого бита должна производиться перед включением асинхронного режима. Если в регистре ASSR конкретной модели этот бит отсутствует, то использование внешнего тактового сигнала с этим микроконтроллером не рекомендуется |

TCNajUB | Состояние обновления регистра TCNTn. При записи в регистр TCNT/i этот флаг устанавливается в 1, а после пересылки записываемого значения в данный регистр флаг аппаратно сбрасывается в 0. Таким образом, сброшенный флаг TCNajUB означает, что регистр TCNTaj готов для записи в него нового значения. Запись в регистр TCNTaj при установленном флаге TCNajUB может привести к повреждению прежнего содержимого регистра и к генерации прерывания |

OCRUB, OCR2AUB, OCR2BUB | Состояние обновления регистра ОСИл (OCR2A/OCR2B). При записи в регистр сравнения соответствующий флаг устанавливается в 1, а после пересылки записываемого значения в регистр флаг аппаратно сбрасывается в 0. Таким образом, сброшенный флаг OCR/iUB (OCR2AUB/OCR2BUB) означает, что соответствующий регистр сравнения готов для записи в него нового значения. Запись в регистр сравнения при установленном флаге OCRUB (OCR2AUB/OCR2BUB) может привести к повреждению прежнего содержимого регистра и к генерации прерывания |

TCR/?UB, TCR2AUB, TCR2BUB | Состояние обновления регистра ТССИл (TCCR2A/TCCR2B). При записи в регистр управления соответствующий флаг устанавливается в 1, а после пересылки записываемого значения в регистр флаг аппаратно сбрасывается в 0. Таким образом, сброшенный флaгTCRлUB (TCR2AUB/TCR2BUB) означает, что соответствующий регистр управления готов для записи в него нового значения. Запись в регистр управления при установленном флаге TCUB (TCR2AUB/TCR2BUB) может привести к повреждению прежнего содержимого регистра и к генерации прерывания |

Примечание, л = 0 для моделей ATmega64x/128x и 2 — для остальных моделей (кроме ATmega8515x).

0 ...

114 115 116 117 118 119 120 ...

195