Раздел: Документация

0 ... 135 136 137 138 139 140 141 ... 195 расположенного по адресу $0Е ($2Е) в моделях ATmega8515x/8535x, ATmegal62x, ATmega8x/16x/32x/64x/128x и по адресу $2D ($4D) — в остальных моделях. Биты с 7-го по 1-й этого регистра доступны только для чтения, а 0-й бит — как для чтения, так и для записи. Формат этого регистра приведен на Рис. 10.3, а назначение его битов описано в Табл. 10.4.

Чтение )/Запись(\Л/) RRRRRRRR/W Начальное значение 00000000 Рис. 10.3. Формат регистра SPSR Таблица 10.4. Биты регистра SPSR

Передаваемые данные записываются, а принимаемые — считываются из регистра данных SPDR. В моделях ATmega8515x/8535x, ATmegal62x, ATmega8x/16x/32x/64x/128x регистр данных располагается по адресу $0F ($2F), а в остальных моделях — по адресу $2Е ($4Е). Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое буфера сдвигового регистра. Другими словами, регистр данных служит буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI. Соединение двух микроконтроллеров (ведущий—ведомый) по интерфейсу SPI показано на Рис. 10.4. Вывод SCK ведущего микроконтроллера является выходом тактового сигнала, а ведомого микроконтроллера — входом. MSB ВЕДУЩИЙ LSB MSB ВЕДОМЫЙ LSB 8-битный сдвиговый регистр MISO MISO 8-битный сдвиговый регистр -X-1— MOSI MOSI Генератор тактового сигнала SPI SCK SCK Разрешение сдвига SS SS Рис. 10.4. Соединение микроконтроллеров по интерфейсу SPI Перед выполнением обмена необходимо, прежде всего, разрешить работу модуля SPI. Для этого следует установить в 1 бит SPE регистра SPCR. Режим работы определяется состоянием бита MSTR этого регистра: если бит установлен в 1, микроконтроллер работает в режиме Master, если сброшен в 0 — в режиме Slave. Передача данных осуществляется следующим образом. При записи в регистр данных SPI ведущего микроконтроллера запускается генератор тактового сигнала модуля SPI, и данные начинают побитно выдаваться на вывод MOSI и соответственно поступать на вывод MOSI ведомого микроконтроллера. Порядок передачи битов данных определяется состоянием бита DORD регистра SPCR. Если бит установлен в 1, первым передается младший бит байта, если же сброшен в 0 — старший бит. После выдачи последнего бита текущего байта генератор тактового сигнала останавливается с одновременной установкой в 1 флага «Конец передачи» (SPIF). Если прерывания от модуля SPI разрешены (флаг SPIE регистра SPCR установлен в 1), генерируется запрос на прерывание. После этого ведущий микроконтроллер может начать передачу следующего байта либо, подав на вход SS ведомого напряжение ВЫСОКОГО уровня, перевести его в состояние ожидания. Одновременно с передачей данных от ведущего к ведомому происходит передача и в обратном направлении, при условии, что на входе SS ведомого присутствует напряжение НИЗКОГО уровня. Таким образом, в каждом цикле сдвига происходит обмен данными между устройствами. Соответственно, в конце каждого цикла флаг SPIF устанавливается в 1 как в ведущем микроконтроллере, так и в ведомом. Принятые байты сохраняются в приемных буферах для дальнейшего использования. В модуле реализована одинарная буферизация при передаче и двойная — при приеме. Это означает, что готовый для передачи байт данных не может быть записан в регистр данных SPI до окончания предыдущего цикла обмена. При попытке изменить содержимое регистра данных во время передачи флаг WCOL регистра SPSR устанавливается в 1. Сбрасывается этот флаг после чтения регистра SPSR с последующим обращением к регистру данных SPI. Соответственно, при приеме данных принятый байт должен быть про читан из регистра данных SPI до того, как в сдвиговый регистр поступит последний бит следующего байта. В противном случае первый байт будет потерян. 10.3. Режимы передачи данных Спецификация интерфейса SPI предусматривает 4 режима передачи данных. Эти режимы различаются соответствием между фазой (момент считывания сигнала) тактового сигнала SCK, его полярностью и передаваемыми данными. Всего существует 4 таких комбинации, определяемых состоянием битов СРНА и CPOL регистра SPCR (Табл. 10.5). Таблица 10.5. Задание режима передачи данных

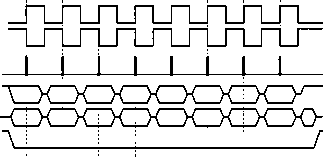

Соответствующие этим режимам форматы обмена данными через SPI приведены на Рис. 10.5 и Рис. 10.6 (передача ведется от старшего бита к младшему). SCK(CPOL = 0) SCK (CPOL =1) Моменты выборок MOSI (от ведущего) MISO (от ведомого) S"S~ (к ведомому) DORD = 0 DORD=1  MSB LSB Бит 6 Бит1 Бит 5 Бит 2 Бит 4 БитЗ БитЗ Бит 4 Бит 2 Бит 5 Бит1 Бит 6 Рис. 10.5. Передача данных при СРНА = 0 LSB MSB 0 ... 135 136 137 138 139 140 141 ... 195 |