Раздел: Документация

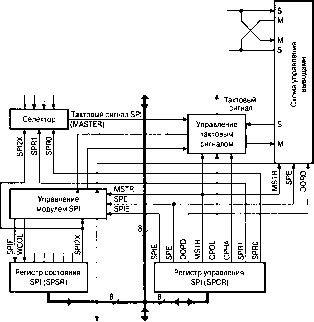

0 ... 134 135 136 137 138 139 140 ... 195 глава 10 Последовательный периферийный интерфейс SPI 10.1. Общие сведения Последовательный периферийный интерфейс SPI (Serial Peripheral Interface), реализованный во всех микроконтроллерах семейства Mega, имеет два назначения. Во-первых, с его помощью может осуществляться обмен данными между микроконтроллером и различными периферийными устройствами, такими как цифровые потенциометры, ЦАП/АЦП, FLASH-ПЗУ и др. Посредством этого интерфейса также может производиться обмен данными между несколькими микроконтроллерами AVR. Использование интерфейса SPI в качестве высокоскоростного канала связи и рассматривается в данной главе. Кроме того, через интерфейс SPI может быть осуществлено программирование микроконтроллера (так называемый режим последовательного программирования). Использование интерфейса SPI в этом качестве будет описано в главе 14. При обмене данными по интерфейсу SPI микроконтроллер AVR может работать как ведущий (режим Master) либо как ведомый (режим Slave). При этом пользователь может задавать следующие параметры: •скорость передачи (восемь программируемых значений); •формат передачи (от младшего бита к старшему или наоборот). Дополнительной возможностью подсистемы SPI является «пробуждение» микроконтроллера из режима Idle при поступлении данных. 10.2. Функционирование модуля SPI Структурная схема модуля SPI приведена на Рис. 10.1. Модуль SPI использует четыре вывода микроконтроллера. Как и в большинстве прочих периферийных устройств, эти выводы являются линиями портов ввода/вывода общего назначения (см. Табл. 10.1). При включенном модуле SPI режим работы указанных выводов (направление передачи данных) переопределяется согласно Табл. 10.2. XTAL Делитель 2/4/8/16/32/64/128

- MISO — MOSI SCK ss Запрос на Внутренняя прерывание от SPI шина данных Рис. 10.1. Структурная схема модуля SPI Таблица 10.1. Выводы, используемые модулем SPI

Таблица 10.2. Переназначение режима работы выводов модуля SPI

Как видно из таблицы, в определенных случаях пользователь должен самостоятельно задать режим работы вывода, используемого модулем SPI, в соответствии с его назначением (см. далее). При этом возможность управления внутренними подтягивающими резисторами выводов, работающих как входы, сохраняется независимо от способа управления их режимом работы. Для управления модулем SPI предназначен регистр управления SPCR. В моделях ATmega8515x/8535x, ATmega 162х и ATmega8x/16x/32x/64x/128x этот регистр располагается по адресу $0D ($2D), а в остальных моделях — по адресу $2С ($4С). Формат этого регистра приведен на Рис. 10.2, а краткое описание функций битов регистра приведено в Табл. 10.3. Подробно использование различных битов регистра будет описано далее. Чтение(Р)/Запись(\Л/) Начальное значение

Рис. 10.2. Формат регистра SPCR Таблица 10.3. Биты регистра SPCR

Контроль состояния модуля, а также дополнительное управление скоростью обмена осуществляются с помощью регистра состояния SPSR, 0 ... 134 135 136 137 138 139 140 ... 195 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||