Раздел: Документация

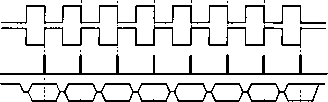

0 ... 136 137 138 139 140 141 142 ... 195 SCK (CPOL = 0) SCK(CP0L=1) Моменты выборок MOSI (от ведущего) MISO (от ведомого) SS (к ведомому)  J DORD = 0: DORD=1: MSB LSB Бит 6 Бит 5 Бит 1 Бит 2 Бит 4 БитЗ БитЗ Бит 4 Бит 2 Бит1 LSB Бит 5 Бит 6 MSB Рис. 10.6. Передача данных при CPHA = 1 Частота тактового сигнала SCK и соответственно скорость передачи данных по интерфейсу определяются состоянием битов SPR1:SPR0 регистра SPCR и бита SPI2X регистра SPSR (Табл. 10.6). Разумеется, речь идет о микроконтроллере, работающем в режиме Master, так как именно он является источником тактового сигнала. Для устройства, находящегося в режиме Slave, состояние этих битов безразлично. Таблица 10.6. Задание частоты тактового сигнала SCK

Примечание./ськ — тактовая частота микроконтроллера. Следует иметь в виду, что работа микроконтроллера в режиме Slave гарантируется только на частотах, меньших или равных /clk/4. 10.4. Использование вывода SS Вообще говоря, этот вывод предназначен для выбора активного ведомого устройства и в режиме Slave всегда является входом. При подаче на него напряжения НИЗКОГО уровня модуль SPI активируется и вывод MOSI переключается в режим вывода данных (если это задано пользователем). Остальные выводы модуля SPI являются в этом режиме входами. А при подаче на вывод SS напряжения ВЫСОКОГО уровня все выводы модуля SPI переключаются в режим ввода данных. При этом модуль переходит в неактивное состояние и прием данных не производится. Как правило, в этом состоянии программа изменяет содержимое регистра данных Следует помнить, что каждый раз, когда на вывод SS подается напряжение ВЫСОКОГО уровня, происходит сброс модуля SPI. Соответственно, если изменение состояния этого вывода произойдет во время передачи данных, и прием, и передача немедленно прекратятся, а передаваемый и принимаемый байты будут потеряны. Если же микроконтроллер находится в режиме Master (бит MSTR регистра SPCR установлен в 1), направление передачи данных через выво-SS определяется пользователем. Если вывод сконфигурирован как выход, он работает как линия вывода общего назначения и не влияет на работу модуля SPL Как правило, в этом случае он используется для управления выводом SS микроконтроллера, работающего в режиме Slave. Если же вывод сконфигурирован как вход, то для обеспечения нормальной работы модуля SPI на него должно быть подано напряжение ВЫСОКОГО уровня. Подача на этот вход напряжения НИЗКОГО уровня от какой-либо внешней схемы будет воспринята модулем SPI как выбор микроконтроллера в качестве ведомого (при этом ему начинают передаваться данные). Во избежание конфликта на шине модуль SPI в таких случаях выполняет следующие действия: 1.Флаг MSTR регистра SPCR сбрасывается, и микроконтроллер переключается в режим Slave. Как следствие, выводы MOS1 и SCK начинают функционировать как входы. 2.Устанавливается флаг SPIF регистра SPSR, генерируя запрос на прерывание от SPI. Если прерывания от SPI разрешены и флаг I регистра SREG установлен в 1, происходит запуск подпрограммы обработки прерывания. Таким образом, если ведущий микроконтроллер использует передачу дан -ных, управляемую прерыванием, и существует вероятность подачи на вход SS напряжения НИЗКОГО уровня, в подпрограмме обработки прерывания от SPI обязательно должна осуществляться проверка состояния флага MSTR. При обнаружении сброса этого флага он должен быть программно установлен обратно в 1 для обратного перевода микроконтроллера в режим Master. ГЛАВА 11 Двухпроводный последовательный интерфейс TWI 11.1. Общие сведения Модуль двухпроводного последовательного интерфейса (Two-Wire serial Interface — TWI) имеется практически во всех микроконтроллерах семейства Mega, за исключением моделей ATmega8515x, ATmega 162х, ATmegal65x и ATmega325x/3250x/645x/6450x. Причем, если в первых двух моделях он отсутствует как класс, то в остальных моделях в режиме двухпроводного интерфейса может работать модуль USI, которому будет посвящена следующая глава. Интерфейс TWI является полным аналогом базовой версии интерфейса 12С фирмы Philips. Он позволяет объединить вместе до 128 различных устройств с помощью двунаправленной шины, состоящей всего из двух линий: линии тактового сигнала (SCL) и линии данных (SDA). Единственными дополнительными элементами для реализации шины являются два подтягивающих резистора, по одному на каждую линию (см. Рис. 11.1). Устройство 1 SDA ч SCL« Устройство 2 Устройство 3 Не- устройство п Рис. 11.1. Соединение устройств с помощью шины TWI Шинные формирователи всех TWI-совместимых устройств выполняются по схеме с открытым коллектором (стоком), что позволяет реализовать функцию «монтажное И». Соответственно, НИЗКИЙ уровень на линии устанавливается тогда, когда одно или более устройств выставляют на линию сигнала лог. О, а ВЫСОКИЙ уровень на линии устанавливается, когда все устройства, подключенные к ней, устанавливают свои выходы в третье состояние. 0 ... 136 137 138 139 140 141 142 ... 195 |