Раздел: Документация

0 ... 105 106 107 108 109 110 111 ... 119 а) Я- СЕ- ь 41555ИЕ10 S -6L >С 1-Р0 Е й СПб Р4 J" Ч с L ЬС 1-Р0 £ й СПб «4 Р4 -Г 1- Ч 2 Z, К РО Л-

СО С£- Ч D Z, >С РО £ в)D СПб Р4 1- СПб Р4 -Г Ч С Z. К РО £

S >С РО Е СПБ Р4 27-4 СПб Р4 -Г D >С РО Е

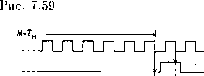

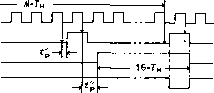

а) н Р. t-  со р13  структурным схемам, приведенным на рис. 7.58. Сигналы загрузки L и выходные сигналы Р12 описываются функциями: L = CE-Qll---Q1~Q~o, Р12 = СЕ Q„ • • • Qx Q0 (рис. 7.59,а), I = CE-Qy-QQo, Р12 = Qn-Q5-q4 (рис. 7.59,6), I = Он • • Qb Qa, Р12 = Qn---Qs-Q4 (рис. 7.59,e). Временные диаграммы для счетчика с последовательным переносом (рис. 7.59,а) показаны на рис. 7.60,а - задержка t"P сигнала Pi2 относительно тактового сигнала вызвана распространением сигнала Р4 через две ИС, причем tp > tP для многокаскадных счетчиков. Временные диаграммы для счетчика с параллельным переносом (рис. 7.59,6) изображены на рис. 7.60,6 - задержка tp сигнала Р12 вызвана распространением сигнала Ps, причем tP > tp для многокаскадных счетчиков, однако задержка сигнала загрузки L определяется исключительно задержкой tp сигнала переноса Р4 относительно тактового сигнала (задержкой сигналов в ЛЭ И-НЕ пренебрегли). Для программирования модуля пересчета можно использовать также вход R сброса счетчика в нулевое состояние (как синхронный, так и асинхронный). Если на синхронный вход сброса R счетчика по mod 16 подать активный уровень в момент времени, когда он находится в состоянии j = €Q3eQ2eq1eQ0, то в следующем такте счетчик установится в состояние j = 0000. Из этого следует, что модуль пересчета счетчика с программированием модуля пересчета с помощью синхронного сброса определяется соотношением M = j + 1(7.37) (при асинхронном потенциальном сбросе модуль пересчета М - j, так как установка нулевого состояния производится немедленно - без участия тактового сигнала). Таблица 7.7. Программирование модуля пересчета

Программирование модуля пересчета можно производить и сигналами R = Qr, так как первый переход состояния каждого триггера QT с 0 на 1 при начале цикла пересчета в нулевом состоянии происходит при достижении в процессе двоичного счета состояния j = Т. В табл. 7.7 указаны модули пересчетов М при R - Qr, из которой видно различие между синхронным и асинхронным входами сброса (555ИЕ18 - счетчик с синхронным входом сброса, 555ИЕ10 - счетчик с асинхронным входом сброса). Счетчик по mod 9 с синхронным сбросом, изображенный на рис. 7.61,я, описывается графом переходов, показанным на рис. 7.61,6". Длительность выходного сигнала Q3 равна периоду тактового сигнала. Если же в этой схеме использовать ИС 555ИЕ10 (счетчик с асинхронным сбросом), то счетчик установится в нулевое состояние сразу же, как только на его выходе появится значение Q3 = 1, а значит, модуль пересчета будет на 1 меньше, чем в предыдущем случае. Длительность сигнала Q3 = 1 определяется быстродействием триггеров счетчика и для ИС 555ИЕ10 составляет примерно 40 не. Достоинством программирования модуля пересчета с помощью сброса счетчика в нулевое состояние является сохранение естественного порядка счета, начиная с нуля, с возрастанием на единицу с каждым тактом числа, выдаваемого счетчиком (в каждом такте производится инкрементирование содержимого счетчика). Кроме того, входы загрузки данных освобождаются для выполнения иных функций. Многокаскадные счетчики с синхронным сбросом программируются, как отмечалось в § 6.7, с помощью адресного компаратора 74ALS677А. Пусть требуется спроектировать счетчик с модулем пересчета М = 64896. Из соотношения (7.37) следует, что j = М - 1 = 64895 = 1111.1101.0111.1111, т. е. для программирования модуля пересчета следует положить R = Аб4895(Л15, • • , Ql, Qo) = = П15П14П13П12П11П10д9П8д7П6П5П4П3П2П1П0. Эту функцию выполняет адресный компаратор при значении кода P3P2PXPq = 0010. Принципиальная схема спроектированного счетчика изображена на рис. 7.62. Сигнал М (Mode - режим) используется для выключения режима программирования (при значении сигнала М - 1 сигнал сброса r = 1 и модуль пересчета равен Л/тах = 216 = 65536). D >1 ->С РО Е 8 СПб С о. о 1 2 3 Р4  Рис. 7.61 3-0 F7-СЕ- S >L ->С Р0 £

«о S >L ->С Р0 Е

S -У1 ->с Р0 £

s -61 ->с Р0 Е

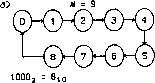

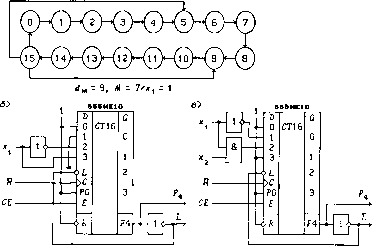

«12 Переключение модулей пересчета двоичных счетчиков. С помощью к управляющих сигналов хь,..., х2 и Х\ можно задать 2к модулей пересчета (к < тп, где тп - число разрядов двоичного счетчика). Для небольшого числа модулей пересчета их переключение осуществляется значительно проще, чем непосредственной загрузкой чисел d\f с возможностью программирования всех модулей пересчета от 2 до 2ТО.  Рис. 7.63 Пример 1. Пусть требуется синтезировать счетчик с двумя модулями пересчета: счетчик по mod 11 при х\ - 0 и счетчик по mod 7 при х\ - 1. Такой счетчик задается графом переходов, приведенным на рис. 7.63,а. На основании соотношения (7.32) составляется таблица истинности (табл. 7.8) для функций D3, D2, Di и D0 (dM = D3D2DiDq), из которой непосредственно следует, что D3 = хь D2 = xu Dx = О, D0 = 1. Принципиальная схема синтезированного счетчика изображена на рис. 7.63,6. Сигнал СЕ используется для разрешения и запрета счета. Пример 2. Пусть требуется синтезировать счетчик с тремя модулями пересчета: счетчик по mod 5 при Х2 = ф и xi - 0, счетчик по mod 7 при х2 - 0 и хх - 1, счетчик по mod 3 при х2 - 1 и xi - 1. На основании соотношения (7.32) Таблица 7.8. Программирование модулей пересчета

составляется таблица истинности (табл. 7.9) для функций D3, D2, Di и Do, из которой непосредственно следует, что D3 = 1, D2 = x2xi, Di = xi, D0 = 1. Принципиальная схема синтезированного счетчика изображена на рис. 7.63,в. Аналогично производится синтез и многокаскадных двоичных счетчиков с переключаемым модулем пересчета. Функциональные устройства на основе двоичных счетчиков. На рис. 7.64 приведены ИС: 74i5590, 74ЛС11590 - счетчик по mod 256 с асинхронным потенциальным сбросом в нулевое состояние значением сигнала R = 0 и выходным синхронным регистром памяти, которые описываются функциями: Р8 = П Qr, DO (7.38) J QRr при OE = 0, r 0I Z-состояние при OE"= 1, где QRr - выходные сигналы триггеров регистра памяти, г = 0,1,..., 7 (рис. 7.65,а); управление сигналом CEN (Clock Enable) выполнено по схеме, изображенной на рис. 7.20,в; 742/5591 - отличается от ИС 74X5590 только функциями DOr = EQRr (сигнал ОЕ следует заменить на Е); 742/5593, 74ЛС11593 - интерфейсное устройство с двунаправленной шиной данных DB7 - DR», содержащее счетчик по mod 256 на Т/D-L-Д-триггерах (7.26) и входной синхронный 0 ... 105 106 107 108 109 110 111 ... 119 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||