Раздел: Документация

0 ... 106 107 108 109 110 111 112 ... 119 ЩсЕМ ю ОЕ

LS593 LSS91 - 00ф - GHD, is - V с LS693 СП 6 RG MUX P4 >CL IE be 1 СЕ* 1 2 Щ

10 - gad, 20 - V ДСП 593 СГ256 rg P8 d 0 1 2 3 L PO E LS691 CT16 rg MUX - >CL RR OE P4 Ю - GMD, 20 ДСП 590 >C PO >Cl OE

GMD, 20 GA/D, 18,13 - V 4-7 - GMD, 13,16 Рис. 7.64 регистр памяти на D-Z-триггерах (рис. 7.65,6), которое описывается функциями: JLГ Qr при 0£= 1,, ъ = до,, ад = { г.сосртояние „;„ 0Е = о, ("9) QRf = DBrLE dHL V QRrLE • dHL, где Qr - выходные сигналы триггеров счетчика (г = 0,1,..., 7); сигнал управления ОЕ = 0Е\ V 0Е2; управление сигналом CEN = CEN\CEN2 выполнено по схеме, изображенной на рис. 7.20,в; (1X5691 - интерфейсное устройство, содержащее счетчик по mod 16 типа 161 (см. рис. 7.46), выходной синхронный ре- сО R >СсГ256 СТИ-ЬСЕН b"-$r СТ- ОГ LS590

db«- не-ег- Е- ->CL tHL RC QR LS593 гт»,. СЕЛ1,- СТ25Б {>С 1 СЕ* 1 1 2 ВТ, oe, PB4- в) P -о £" R-HE- д-

LS691

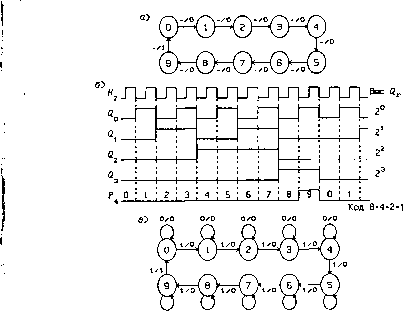

Рис. 7.65 гистр памяти с асинхронным потенциальным сбросом значением сигнала RR = 0 и 4-разрядный мультиплексор 2 -► 1 (рис. 7.65,в), которое описывается функциями: DOr J QrA V QRT А при ОЕ = О, [ Z-состояние при ОЕ = 1, QR+ = (QrdHL V QRrdHL) RR, г = 0,1,2,3; (7.40) 74X5693 - интерфейсное устройство, содержащее счетчик по mod 16 типа 163 (см. рис. 7.46), выходной синхронный регистр памяти с синхронным сбросом значением сигнала RR = О и 4-разрядный мультиплексор 2 -► 1 (рис. 7.65,в), которое описывается Аункпиями 7.40 и QR? = QrRR • dHL V QRTdIIX, г = 0,1,2,3. Каскадирование ИС 74LS590 показано на рис. 7.66,а, из которого на основании одного из соотношений (7.38) следует, что сигналы переносов 71523 Ps = П Qr, Pie = П Qr, Р24 = П Qr, r=0r=Sr=16 a = P8 V P16 = Ts~PT&, a = П Or- r=0 Сигнал переноса а = Лб5535 (0л5, • • •, Q\, Qo) обеспечивает двоичный счет в трехкаскадном счетчике. Выходы с тремя состояниями D023 ~ DOq позволяют использовать рассмотренный счетчик по mod 224 в качестве внешнего устройства микроконтроллеров и микроЭВМ. Сигнал СЕ (Count Enable) используется для включения и выключения счета. Использование ИС 74L5593 в качестве интерфейсного устройства микроконтроллеров, построенных на основе микропроцессора 580ВМ80, приведено на рис. 7.66,5. Сигнал L асинхронной потенциальной загрузки данных QRr (г = 0,1,..., 15) из регистров памяти в счетчики (см. рис. 7.65,6) на основании (7.39) с учетом стробирования тактовым сигналом Н можно представить в виде: L = P8VP16vF = Р8Р16Н, L = Н fi Qr = A65535(Ql5,...,Ol,Oo) r=0 (стробирование введено для исключения ложных значений сигнала L = 0, которые могут возникнуть при переходных процессах). Таким образом, данное интерфейсное устройство представляет собой счетчик с программируемым модулем пересчета М. Отличие асинхронной загрузки от синхронной заключается в выполнении ее на один такт раньше, т.е. в том же такте, в котором формируется значение сигнала загрузки L = 0, а не в следующем такте, как при синхронной загрузке. Исходя из этого, на основании соотношений (7.33) получим: M = 2m-\-dM, 0<dM <2m-3.(7.41) Структура системных шин на рис. 7.66,6 показана для случая использования микропроцессора 580ВМ80 (DB - Data Bus, АВ - Address Bus, CB - Control Bus, I/ORD - I/O Read, I/OWR - I/O Write, CSk - Chip Select). Программируется модуль пересчета записью в регистры памяти двухбайтового числа d\f = jwiAfo = 2m - 1 - Л/. Младший d\fo и старший d\n байты числа d\f, поступающие последовательно от микропроцессора но шине данных DB при выполнении команд программы со D0-7 74LS390 8 *>1! ст- 5- 4*1 -6CEN СТТ8 RG ->CL CZ СО > DB С св: 775ЕВ l 1 DO 1-1 74LS390 8 >С сТТ8 DO, 74LS390 8 . L->C -6СЕМ СГТ8 RG DO rt - p 8-bit System Data Bus ГТТ 773555 CL > oLE CTfB RG 1 CEN 1 1- 2 1 OE . 1 M 2 Dl 5?, iLE CTfB RG 1 CEN 1 2 1 OE 4 1 i- 2 D2 р&]--ГТ Рис. 7.66 MVI A, dMQ; загрузка в аккумулятор А младшего байта do OUT P-CSl; вывод djo из аккумулятора А в порт PjCSI MVI A,dM\; загрузка в аккумулятор А старшего байта di OUT P.CS2; вывод &мi из аккумулятора А в порт PJCS2, записываются в регистры памяти переходом сигнала I/OWR с 0 на 1 при значениях адресных сигналов CSi = 0 и CS2 = 0, выдаваемых дешифратором портов внешних устройств (8-разрядные двоичные опе- „ . JJD /-*сл .. D ЛСП ..... ассемблера). Чтение состояния счетчика производится по шине данных DB сигналами a = I/ORD V CSi = I/ORD CSX, /3 = I/ORD V CS2 = I/ORD CS2 при выполнении команд ввода IN PS!SI; ввод в аккумулятор А состояния счетчика Dl MOV В, А; пересылка данных из аккумулятора А в регистр В IN P.CS2; ввод в аккумулятор А состояния счетчика D2 программы обслуживания внешнего устройства, выполняемой микропроцессором. При использовании только аппаратных выходов L и Pie внешнее устройство будет представлять собой делитель частоты с программируемым коэффициентом деления (ЛЭ ИЛИ а и /3 при этом можно исключить). Длительность активного уровня сигнала Р\е = О составляет 255, 5 Т# при модулях пересчета М > 256 (при значениях М < 256 сигнал Р\ъ = 0, но при этом нет смысла использовать две ИС 74L5593; Тн - период тактового сигнала Я), а длительность значения сигнала загрузки L = 0 определяется исключительно временем переходного процесса (30 - 40 не), вызываемого в середине такта воздействием сигнала L = PgPieB. Сигнал L можно использовать в качестве выходного сигнала делителя частоты при любых модулях пересчета, но следует помнить, что он имеет малую длительность. 7.6. Синхронные двоично-десятичные счетчики Синтез и основные свойства синхронных двоично-десятичных счетчиков были рассмотрены в § 4.5. Граф переходов счетчика по mod 10 изображен на рис. 7.67,а {-/Ра = -/0 и -/1, Р4 - сигнал переполнения счетчика). Этому графу переходов соответствуют функции возбуждения (4.38) Т-триггеров: T0 = 1,T1 = Q3Q0,T2 = Q1Q0, ) Тз = q2q1q0 v Q3Q0, Ра = q3q0. j{ На рис. 7.67,5 показаны временные диаграммы синхронного счетчика по mod 10, соответствующие графу переходов, изображенному на рис. 7.67,а. Внутренние состояния счетчика V = (лз,П2,лъло) обозначены числами j = eQ3eQ2eQ1eQo = 0,1,..., 9, где egr = 0 или 1 - состояние триггера QT (г = 0,1,2,3). Граф переходов счетчика по mod 10, функции возбуждения триггеров которого Т„ = Го, Т, = P0Q3no, Т2 = PoQjQo, Т3 = P0Q2Q1Q0 V P0Q3Q0, Ра = P0Q3Qo,  0/-00/-0ОО0/-00/-0 Рис. 7.67 изображен на рис. 7.67,e (Р0 - сигнал разрешения счета и переноса; Ро/Ра = 0/0, 1/0 и 1/1). При значении сигнала управления Р0 = 0 состояния счетчика не изменяются, что указывается на графе переходов петлями Pq/Pa = 0/0. Двоично-десятичные счетчики. Каждой ИС 4-разрядного синхронного двоичного счетчика, кар; правило, соответствует идентичная по цоколевке и функциональному назначению (кроме модуля пересчета) ИС двоично-десятичного счетчика. Функции возбуждения Тт триггеров счетников, обладающих наибольшими функциональными возможностями, как и в двоичных счетчиках, реализуются с предоставлением пользователю управления ими с помощью двух внешних сигналов Ро и Е - РпЕ -Тт для всех триггеров счетчика. При этом сигнал переноса счетчика описывается функцией Ра = Е Q3Qo-(7-43) Двоично-десятичные счетчики могут иметь и последовательный перенос: RC= РоЕ-РаН = PnEQ3QoH.(7.44) 0 ... 106 107 108 109 110 111 112 ... 119 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||