Раздел: Документация

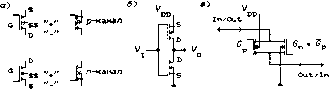

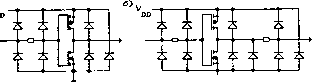

0 ... 44 45 46 47 48 49 50 ... 119 SSI - Small-scale integration (малая степень интеграции), MSI - Medium-scale integration (средняя степень интеграции), LSI - Large-scale integration (большая степень интеграции), VLSI - Very-large-scale integration (сверхбольшая степень интеграции). Деление ИС на классы по числу компонентов, в них содержащихся, достаточно условно и может со временем изменяться. 5.2. Интегральные схемы КМОП серий Для проектирования цифровых ИС кроме биполярных п-р-п- и p-n-p-транзисторов используются также униполярные полевые п- и р-канальные транзисторы (рис. 5.17,а), которые называются МОП-транзисторами (МOS-transistors; MOS - Metal-Oxide-Semiconductor - металл-окисел-полупроводник). В общем случае полевой транзистор имеет четыре электрода: исток S (Source), сток D (Drain), затвор G (Gate) и подложка SS (Substrate). Вывод затвора в изображении полевых транзисторов смещается ближе к истоковому выводу. Изображение канала с обогащением штриховой линией символизирует отсутствие проводимости между стоком и истоком при нулевом напряжении затвор-исток. На рис. 5.17,а символами "+" и "-" обозначены полярности напряжений на электродах для нормального режима работы полевого транзистора. Подложка SS обычно подключается к истоку или к одному из полюсов источника питания.  Рис. 5.17 На рис. 5.17,6 показана схема включения пары комплементарных транзисторов (транзисторов с разными типами каналов), представляющая собой электронный ключ - инвертор (ЛЭ НЕ). Особенностью данного ключа является отсутствие тока через транзисторы в статическом состоянии, так как при любом значении входного сигнала один из последовательно включенных транзисторов закрыт. Ключ потребляет ток только при его переключении на интервале времени, в течение которого изменяется входной сигнал. На этом интервале оба транзистора J открыты, так как входной сигнал имеет значения 0 < V/ < Vdd? ято приводит к значениям разностей напряжений между затворами и истоками п- и р-канальных транзисторов, значительно отличающимися от нулевых. Наибольший ток протекает при р/ = Vdd/2. Полевые транзисторы позволяют построить не только цифровые, но и аналоговые ключи для коммутации двуполярных налоговых сигналов, что невозможно сделать на биполярных транзисторах. На рис. 5.17,в показан основной элемент такого аналогового ключа (вместо потенциала земли для коммутации двуполярных сигналов следует подать отрицательное напряже-иие Vee)- При значениях Gv = Vdd и Gn = Vee оба транзистора закрыты (сопротивление Roff закрытого ключа составляет £отни МОм) - ключ разомкнут, а при Gv = Vee и Gn = Vdd открывается один из транзисторов в зависимости от полярности Коммутируемого входного напряжения Vee < V/ < Vdd- В этом гслучае сопротивление между полюсами ключа In/Out и Out/In составляет от единиц до сотен Ом в зависимости от типа клю-ряа (сопротивление Ron открытого ключа). Чем меньше зависимость величины Ron от напряжения коммутируемого сигнала, тем выше линейность ключа. При проектировании аналоговых ключей принимают меры по улучшению их линейности. Вход In/Out и выход Out/In у аналогового ключа неразличимы - входом будет тот полюс ключа, на который подан коммутируемый сигнал. Разработаны три основные технологии изготовления ИС на полевых транзисторах: га-МОП технология (n-MOS technology), р-МОП технология (p-MOS technology), КМОП технология (CMOS technology; CMOS - Complementary MOS). Все эти технологии постоянно совершенствуются с целью Увеличения быстродействия и степени интеграции элементов на жристалле. К настоящему времени разработано несколько десятков этих технологий. Схемотехника КМОП ИС. Первые КМОП ИС серии C.D4000 были разработаны фирмой RCA в 1968 г. [26], затем была выпущена серия CD4000A, вытесненная впоследствии (1976 г.) серией С1)40002? с улучшенными характеристиками. Данные £ерии ИС выпускают многие зарубежные фирмы, например, Motorola (ИС серии МС14000Б), National Semiconductor (ИС серии CD4000B), Phillips Components (ИС серии NEF4000B), SGS-Ates (ИС серий НСС4000В/НСР4ШВ) и др. Общим не- достатком ИС всех этих серий является их низкое быстродействие (время задержки сигналов tpd достигает сотен не) и малые значения выходных токов. В 1981 г. фирмами Motorola и National Semiconductor были разработаны ИС серий 54НС/74НС {НС - High speed CMOS), близкие по физическим параметрам к сериям 54LS/74LS. В частности, быстродействие этих КМОП и ТТЛ серий одинаково (среднее время задержки вентиля tpd = 10 не). Еще большее быстродействие было достигнуто в КМОП сериях 54АС/74АС (АС - Advanced CMOS), разработанных в 1985 г. фирмой Texas Instruments Inc. (tpd = 3,5 не). Положительные свойства как ТТЛ ИС, так и КМОП ИС были реализованы фирмой TI в ИС серии ВСТ (1987 г.), изготовляемых по БгСМОб-технологии (Bipolary CMOS TTL Compatible input - технология с размещением биполярных и КМОП транзисторов на одном кристалле с уровнями входных и выходных сигналов ИС, совместимых с ТТЛ-уровнями) [27]. В табл. 5.9 приведено соответствие отечественных и зарубежных серий КМОП ИС. Напряжение питания у КМОП ИС можно изменять в широких пределах - чем выше напряжение питания, тем больше быстродействие ИС. По выполняемым функциям и (или) нумерации выводов ИС серий 4000 в большинстве своем отличаются от ТТЛ ИС аналогичного функционального назначения. Функциональный ряд ИС серий 54НС/74НС включает в себя часть ИС как ТТЛ серий 54/74, так и КМОП серий 4000 (ИС с одинаковыми номерами во всех этих сериях имеют одинаковое функциональное назначение и нумерацию выводов). На рис. 5.18,а показаны цепи диодной защиты входов и выходов ЛЭ от электростатического напряжения у ИС серии CD4000A, а на рис. 5.18,6- у ИС серии CD4000J9. Такую защиту входов и выходов имеют все цифровые ИС, кроме преобразователей уровней напряжений CD4049UB (561ЛН2) и CD4050B (561ПУ4), у которых используется другое вариант защиты входов (рис. 5.19). При первом варианте защиты входов уровни входных сигналов не должны превышать напряжения питания Vdd из-за открывания диода, включенного между входом и полюсом Vdd- При втором варианте защиты уровни входных сигналов могут в несколько раз превышать значение Vdd, не выводя ИС из строя (избыточное напряжение гасится на резисторе). В этом случае ИС работает как понижающий преобразователь уровня логической 1. Входная цепь обеспечивает также защиту от отрицательных значений напряжений входных сигналов. В Таблица 5.9. Соответствие отечественных и зарубежных КМОП серий

СИхххД о) l/e CM049W CDixxxS Рис. 5.18 в) cd 1/6 cw0s0b м у = х Рис. 5.19 Пгжыии! Г. И., Ноисмьаеы Т. Я. дальнейшем цепи защиты входов и выходов, как правило, показываться не будут. Различие между сериями CD4000A (рис. 5.19,а) и CD4000B (рис. 5.19,6) заключается в наличии на выходах ИС последней дополнительных буферов для развязки ИС от внешней среды. Вместо серии CD4000A в настоящее время выпускается серия CD4000UВ с небуферированными выходами, имеющая аналогичные электрические параметры (UВ - Unbuffered, В - Buffered). Наличие в серии CD4000J9 дополнительных выходных буферов приводит к увеличению задержек сигналов в ЛЭ, но улучшает переключательные характеристики. Сравнительная характеристика этих серий приведена в табл. 5.10. Таблица 5.10. Параметры ИС серий CD4000B и CD4000UB

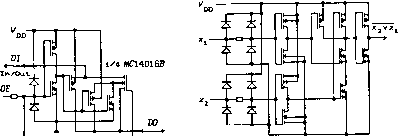

Реализация аналогового ключа MC14016J5 показана на рис. 5.20. При значении сигнала ОЕ = 1 (ОЕ - Output Enable) ключ открыт, а при ОЕ = 0 - закрыт. В закрытом состоянии ключ характеризуется большим выходным импедансом и принято говорить, что выход находится в Z-состоялии. Вместо потенциа-  Out/ini/4 CD4QQ1S Рис. 5.20Рис. 5.21 ла земли можно подать отрицательное напряжение Vee-i но пРи этом должно выполняться условие Vdd - Vee < 15 В. Схема двухвходового ЛЭ ИЛИ-НЕ CD4001J? представлена на рис. 5.21. Выходной каскад на двух комплементарных транзисторах является буферным каскадом, так как он изолирует все внутренние связи от выхода ЛЭ. Различие между небуферированной (UB) и буферированной (В) сериями наглядно видно из рис. 5.22, где представлены ЛЭ MC140UUB и МС14011Я, выполняющие одинаковые функции 2И-НЕ. Другое схемотехническое исполнение ЛЭ 2И-НЕ показано на рис. 5.23. Универсальный набор элементов, состоящий из двух комплементарных пар МОП-транзисторов и инвертора, реализован в ИС CD4007UB (рис. 5.24). Данный набор позволяет пользователю с помощью внешних соединений выводов ИС получать аналоговые коммутаторы и ЛЭ: аналоговый двухканальный коммутатор (рис. 5.25) - соединены выводы 2 и 9; 4 и 11; 3 и 6; 8, 10 и 13; 1, 5 и 12; три инвертора - соединить выводы 2, 11 и 14; 4, 7 и 9; 8 и 13 (выход НЕ со входом 6); 1 и 5 (выход НЕ со входом 3); 10 - вход НЕ, 12 - выход НЕ; ЗИЛИ-НЕ - соединить выводы 4, 7 и 9; 2 и 13; 1 и 11; 5, 8 и 12 (выход ЛЭ со входами 3, 6 и 10); ЗИ-НЕ - соединить выводы 2, 11 и 14; 4 и 8; 5 и 9; 1, 12 и 13 (выход ЛЭ со входами 3, 6 и 10); ЛЭ, реализующий функцию / = x\(x2V х3) - соединить выводы 2 и 14; 4, 8 и 9; 1 и 11; 5, 12 и 13 (выход /; 6 - хх, 3 - х2, 10 - х3); ЛЭ, реализующий функцию / = Х\Х2 V х3 - соединить выводы 2 и 14; 7 и 9; 4 и 8; 1, 11 и 13; 5 и 12 (выход /; 6 - хь 3 - *2, ю - *3); инвертор с Z-состоянием выхода, выполняющий функцию 0 ... 44 45 46 47 48 49 50 ... 119

|