Раздел: Документация

0 ... 46 47 48 49 50 51 52 ... 119 р-канального и n-канального транзисторов). Зарубежные ЛЭ, не имеющие в настоящее время отечественных аналогов, показаны на рис. 5.31 и 5.32. CD4071B 1 2 1 CD4072B НС4072 2 1 Li£ 12. TP 7 - GND dd CD4DB5B

7 1 4 GND V 1 e,8 - NC 7 - GND »• " Vr.r. dd CD40B6B

CD4073B CD4075B HC4075

7 14 GND dd HC5B 7 - GND 14 - V

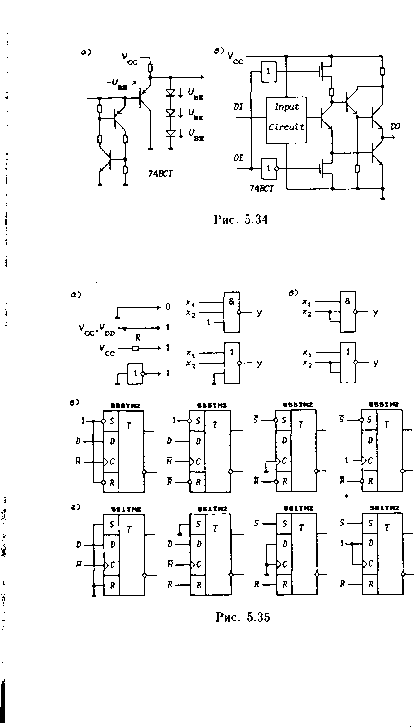

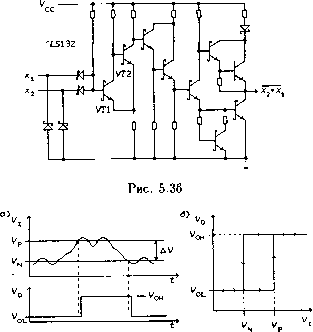

GND 14 - V. 4 7 14 NC GND vdd CD4082B 4 3 9 I 12 тшс 7 - gm> 14 - V dd Рис. 5.32 Параметры ИС КМОП серии 74НС приведены в табл. П2.1 и П2.2 [27, 39], а в табл. П2.3 - параметры ИС серий 4000 [40, 41], которые в первую очередь следует учитывать при проектировании цифровых и микропроцессорных устройств. Параметры отечественных ИС серий 176, 561 и 1561 можно найти в справочниках [35, 42, 43], а ИС серии 1554 - в [34]. Полезный справочный материал по ИС КМОП серий имеется в [44]. Интегральные схемы серий 54ЛС11000/74АС11000. Для уменьшения уровня помех у быстродействующих КМОП ИС, возникающих при переключении ЛЭ, предпочтительнее использовать центральное расположение выводов питания на кристалле, причем выходы ИС следует располагать на той стороне, где находится общий вывод питания (GND). Фирма TI выпустила серии ИС SN54ACllx х x/5iV74ACrlx х х и 5iV54AC7ilxxx/5./V74AC7ilxxx, где число 11 указывает на центральное расположение выводов питания ИС, а числа ххх - порядковый номер ИС, как и в остальных сериях SN54/SN74. На рис. 5.33 приведены ЛЭ этих серий. Интегральные схемы серий SN54BCT/SN74BCT. Как указывалось выше, ИС данных серий изготовляются по BiMOS технологии. Входные цепи ИС выполняются по схеме, приведенной на рис. 5.34,а, что делает входы этих ИС совместимыми с ТТЛ-уровнями входных сигналов. В микропроцессорных системах в большом количестве используются шинные драйверы и приемопередатчики, причем в каждый момент времени в активном состоянии находится приемопередатчик или драйвер только одного внешнего устройства, а остальные - в Z-состоянии. Драйверы и приемопередатчики, выполняемые по ТТЛ технологиям, в Z-состоянии выходов потребляют ток того же порядка, что и в активном состоянии выходов, хотя не выполняют большую часть времени полезной работы. Основная цель разработки BiMOS ИС и заключалась в резком снижении потребляемого тока в Z-состоянии выходов ИС, предназначенных для проектирования внешних устройств микропроцессорных систем. На рис. 5.34,6показана схема ЛЭ с Z-состоянием выхода, выполненного по BiMOS технологии (Input Circuit - входная цепь, показанная на рис. 5.34,а). Неиспользуемые входы ИС. При проектировании цифровых устройств на ИС могут использоваться не все их входы. Исходя из логики работы разрабатываемого устройства, на эти входы следует подать либо логический уровень 0, либо уровень 1. Логический уровень 0 как в ТТЛ, так и в КМОП ИС подается подключением неиспользуемого входа к корпусу (О В). Логический уровень 1 подается на неиспользуемые входы подключением их к источнику напряжения питания Vcc (ТТЛ И С) или Vdd (КМОП ИС), однако входы ТТЛ ИС серий 54/74, 54L/74L, 54Я/74Я и 545/745, в которых используются многоэмиттерные транзисторы, рекомендуется подключать к источнику питания через токоограничивающий резистор для защиты от скачков напряжения, возникающих, например, при включении питания. Способы подачи на входы ИС констант 0 и 1 изображены на рис. 5.35,а (логический уровень 1 можно подавать с выходов ЛЭ, если некоторые из них остались в устройстве неиспользованными). Величина резистора определяется из соотношения Дтвх = (Vcc - VlHmin)/n 1щ, ал 1000 лс11002 2 7? 1 тт 1 дсп 004 20 лсп 008 I I 2 лсп 01 о леи 011 & - - & & 4,5 - GHD - Vcc лс11020 4,з - GHD лсп 021 14,17 - НС 4,3- GHD 4-7 - GHD 12,13 - v 4,3 - GHD 4,5 - GHD & лсп 027 2 Т 1 8,14 - НС 4 - ghd 11 - v лсп 051 8,14 - НС ч - GHD лсп 030 з 2 1 14 1 3 12 а 12,13 лсп 032 12,13 - v - 1 1 б 6,7,10 - НС 4 - GHD ЙС\ 20 034 лсп 064 GHD 11 - v 4,3 - ш> лсп 086 1 is 4,3 - GHD >2,13 - v 14,17 4-7 - НС GHD =1 лсп 800 2 лсп 802 сс лсп 810 23 22 4,3 - GHD ±э 12,13 -1 2 1> 1» =1 •=1 GHD 12,13 GHD GHD; ii - v  где п - число подключенных к резистору входов ЛЭ. У многовходовых ЛЭ И, ИЛИ, И-НЕ и ИЛИ-НЕ неиспользуемые входы можно подключать к используемым (рис. 5.35,6). Если какой-либо вход ИС, выполненной по ТТЛ-технологии, не подключен ни к корпусу, ни к источнику питания, то она будет работать так, как будто на этот вход подан логический уровень 1, но надежность работы будет низка (импульсные помехи, вызванные переключением соседних входов и выходов, могут привести к непредусмотренному срабатыванию ИС). На рис. 5.35,6 показаны различные варианты включения ТТЛ jD/.ft-5-триггера при неполном использовании его функциональных возможностей, определяемых функцией переходов Q+ = 5 V [D dH V Q dH) R. Если тактовый сигнал Н = const (0 или 1), то dH = 0, и никакие помехи на информационном входе D не могут вызвать ложного срабатывания асинхронного потенциального Д-5-триггера, описываемого функцией переходов Q+ = 5 V Q R. Из этого следует, что в этом случае вход D можно оставить неподключенным к полюсам источника питания. Соответствующие варианты включения КМОП £>/Я-5-триггера при неполном использовании его функциональных возможностей показаны на рис. 5.35,г - у КМОП ЙС не рекомендуется оставлять неподключенным ни одного неиспользованного входа из-за открывания входной комплементарной пары транзисторов, что приводит к протеканию большого сквозного тока и резкому увеличению потребления мощности в статическом режиме. 5.3. Триггеры Шмитта Схемы, имеющие разные уровни включения и выключения (пороги срабатывания), называются триггерами Шмитта. Интегральные триггеры Шмитта выполняют, кроме того, функцию ЛЭ НЕ, И-НЕ, ИЛИ-НЕ (инвертирующие триггеры Шмитта) или И, ИЛИ (неинвертирующие триггеры Шмитта). Инвертирующий триггер Шмитта 5741-5132, на входе которого включен ЛЭ 2И, а на выходе - ЛЭ НЕ, изображен на рис. 5.36. Разные уровни срабатывания в этой схеме обеспечиваются усилителем с обратной связью по току, выполненным на транзисторах VTI и VT2. На рис. 5.37,а показаны временные диаграммы формирования неинвертирующим триггером Шмитта выходного сигнала Уо с крутыми фронтами из медленно меняющегося входного напряжения V/. Выходное напряжение триггера Vo скачком изменяется с 0 на 1 при достижении входным напряжением V/ верхнего порога Vp и скачком изменяется с 1 на 0 при пере-  гис. О.HI сечении входным напряжением нижнего уровня VV, т.е. триггеры Шмитта имеют два устойчивых состояния, но в отличие от триггеров, рассмотренных в § 3.3, они имеют один вход и могут управляться как цифровым, так и аналоговым сигналом (под цифровыми сигналами понимаем сигналы, имеющие фронты малой длительности, а под аналоговыми - сколь угодно медленно изменяющиеся сигналы). На рис. 5.37,6показана передаточная характеристика (петля гистерезиса) триггера Шмитта. Разность уровней AV - Ур - Уы называется шириной петли гистерезиса. Триггеры Шмитта часто используются для формирования прямоугольного напряжения из синусоидального, а также для фильтрации помех в линиях связи, величина которых не превышает значения АУ. В частности, для увеличения помехозащищенности И С на некоторых их входах устанавливаются встроенные триггеры Шмитта. На рис. 5.38 представлены триггеры Шмитта как отечественного, так и зарубежного производства. Если триггер Шмитта 0 ... 46 47 48 49 50 51 52 ... 119

|