Раздел: Документация

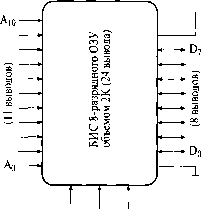

0 ... 9 10 11 12 13 14 15 ... 39 Назначение выводов 8-разрядного ОЗУ объемом 2К +5 В  CS ОЕ WE Аю-..Ao: указывают адреса ячеек памяти (всего 2К = 2П) D7...D0: передают 8-разрядные данные CS: при «О» ОЗУ действует ОЕ: если сигнал равен «О», обмен данными разрешен WE: если сигнал равен «О», разрешена запись данных  Рис. 4.13. Цоколевка БИС ОЗУ На Рис. 4.14 представлен вариант размещения адресов БИС каждой из микросхем памяти, показанных на Рис. 4.11. Области А и В соответствуют двум ПЗУ по 2 Кбайта, а области С и D - двум схемам ОЗУ. Такая схема называется картой памяти. Мы определили область адресов одной из БИС ОЗУ в пределах 8000H...87FFH. Теперь подумаем, как соединить микросхему ЗУ с процессором. Для этого обратимся к Рис. 4.15. Очевидно, что, когда шестнадцатеричный адрес в пределах от 8000Н до 87FFH представлен двоичными 16-разрядными числами с разрядами Ao...Ai5, при обращении к соответствующим ячейкам памяти меняются только младшие 11 разрядов (Ао...Аю), а старее ============================-============-=-== Шестнадцатеричный адрес

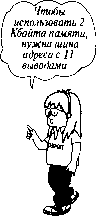

Обозначения на Рис. 4.11 ® © Х § е Эта схема называется картой памяти Рис. 4.14. Распределение адресов для четырех БИС ЗУ Шие разряды (AY j.-.Ajs) остаются без изменения. В этом случае при запросе процессором ячеек памяти ОЗУ значения в старших раз-Рядах (Ai5...An) 16-выводной адресной шины (А15...А0,) будут постоянны, образуя одно и то же двоичное число «10000». Таким образом, мы определили область памяти, то есть диапазон адресов, По которым процессор вызывает содержимое ячеек памяти ОЗУ --- =-===============- 89

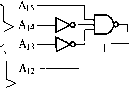

Рис. 4.15. Изменяющиеся и неизменяющиеся разряды в области адресов 8000H...87FFH объемом 2 Кбайта. Иными словами, когда старшие разряды (Ai5--.An) адресной шины установлены в состояние «10000», становится возможным соединение процессора именно с рассматриваемой нами БИС ОЗУ емкостью 2 Кбайта. На Рис 4.16 показан один из способов схемотехнической реализации соединения БИС ОЗУ с ЦПУ. Мы остановились на варианте схемы выборки адреса, построенной на основе вентиля «И-НЕ» и 2-разрядного дешифратора. Как видно из Рис. 4.16, 11 младших разрядов адресной шины (выводы Ао...А10 процессора) непосредственно соединены с выводами Ао...Аю ОЗУ. Когда на входах А15, А14 и А13 3-входовой логической схемы выборки, собранной на вентиле «И-НЕ» и двух инверторах, устанавливается состояние «100», на вход G 2-разрядного дешифратора подается «0», и дешифратор активизируется. Мы знаем, что в зависимости от комбинации сигналов на входах А и В дешифратора на одном из его четырех выходов (Y0...Y3) устанавливается сигнал «0». В рассматриваемом примере значение сигнала на выходе Y0 станет равным «0» только в том случае, если оба входа, соответствующие разрядам А,2 и Ai,, одновременно будут находиться в состоянии «0». Таким образом, на выходе Y0 «0» появля- ( Схема подключения ОЗУ, занимающего область адресов 8000Н... 87FFH ) 3-входовый вентиль «И-НЕ». Только когда на выходах 151413 ~ «100», mG - «0» 2-разрядный дешифратор. Дешифратор в активном состоянии, только когда сигнал на выводе Gравен «О». Сигнал на выходе Y0 равен «0», только когда входы An, А\ 1 находятся в состоянии «00»  Ап

А Если вместо вывода Y1 использовать Y0, то можно выбрать адреса из области 8800H...8FFFH Сигнал выборки адреса 2-входовой вентиль «И-НЕ». Сигнал на выводе>МКЕ() CSравен «О», только когда оба сигнала (Y0u MREQ) равны «0» ОЗУ2КХ 8 бит. ОЗУ в активномсостоянии, когда сигнал CSравен «0». Когда сигнал RDравен «О», данные считываются; когда сигнал WR равен «О», данные записываются  Рис. 4.16. Схема соединения БИС ОЗУ с ЦПУ ется только тогда, когда старшие разряды адресной шины (AI5...Ai i) имеют значение «10000». Однако только этих условий недостаточно для того, чтобы процессор мог производить операции считывания или записи в ОЗУ. Интегральная схема ОЗУ должна находиться в активном состоянии при обращении к ней процессора, для чего с вывода М REQ процессора должен поступить сигнала «0». Проверку выполнения этого условия осуществляет вентильная схема, собранная на 2-входовом логическом элементе «И-НЕ». На один вход вентильной схемы подается сигнал с вывода MREQ процессора, а на второй - с выхода Y0 дешифратора. Если эти сигналы одновременно равны «0», на вывод CS устройства памяти поступает сигнал «0», который и активи- зирует БИС ОЗУ. Так, выбрав на адресной шине один из адресов в диапазоне от 8000Н до 87FFH и послав сигнал «О» с вывода MREQ, процессор обращается к определенной ячейке памяти, расположенной в БИС ОЗУ, имеющей объем 2 Кбайта. Восемь выводов шины данных (D7...D0) ОЗУ и процессора соединены непосредственно. Режим работы ОЗУ (считывание или запись) определяется сигналами RD и WR, поступающими от процессора соответственно на входы о! (Output Enable) и wi (Write Enable), разрешающие считывание или запись. Итак, мы подключили одну из БИС памяти к ЦПУ. Посмотрите еще раз на Рис. 4.16 и проследите порядок прохождения сигналов. Разобравшись в том, как работает одна БИС ОЗУ, перейдем к следующей БИС например, ОЗУ, адреса которого представлены на карте памяти (Рис. 4.14) областью D. Эта область является продолжением области адресов первой БИС - от 8800Н до 8FFFH. Для нее значащие цифры пяти старших разрядов (А15...АП) адресной шины образуют двоичное число «10001» (Рис. 4.15). Как вы думаете, с какого выхода дешифратора (Рис. 4.16) нужно снять сигнал управления второй БИС ОЗУ? Очевидно, с того выхода, на котором значение сигнала равно «0», когда в пяти старших разрядах адресной шины установлено число «10001», то есть с выхода Y1. Активизацию второй БИС ОЗУ по сигналу процессора целесообразно осуществлять с помощью точно такой же схемы выборки, как и в первом случае. Дешифратор, показанный на Рис. 4.16, имеет всего четыре выхода, что позволяет использовать его для построения ОЗУ, состоящего из четырех аналогичных БИС. Соединение ЦПУ с портами ввода-вывода В качестве портов ввода-вывода микрокомпьютера часто используются БИС универсального назначения, которые могут программироваться и как порт ввода, и как порт вывода. В числе таких ИС можно упомянуть, например, схемы серий РЮ, PIA и PPI, которые мы рассмотрим более подробно в восьмой главе. Здесь же, в целях изучения самого принципа построения простейших портов  ввода-вывода, посмотрим, как это можно сделать на основе 8-разрядной защелки (74LS373), описанной в предыдущей главе. Зададим область адресов портов ввода-вывода, подключенных к микрокомпьютеру, в диапазоне от 00 до FF в шестнадцатеричной системе (то есть от 0 до 255 при переводе в десятичный формат). Сигналы обращения процессора к определенным адресам портов ввода-вывода так же, как и в случае ОЗУ, передаются по адресной шине. Все адреса портов в области от ООН до 0FFH могут быть представлены 8-разрядными двоичными числами, поэтому для них достаточно использовать только 8 младших разрядов адресной шины (A7...Aq). На Рис. 4.17 показаны схемы портов ввода и вывода, выполненных на 8-разрядных ИС регистра-защелки 74LS373. Как отмечалось выше, схемы данной серии относятся к электронным устройствам с Z-состоянием. Это означает, что при значении входного сигнала на выводе ОС, равном «1», выходная цепь схемы отключается от внешних устройств, точнее, переходит в высокоомное («Z») состояние. Когда входной сигнал на выводе G соответствует «1», 8-разрядные данные передаются с входов на выходы схемы. При переключении входа G из состояния «1» в состояние «0» передача данных прекращается. Текущие значения данных «защелкиваются» (записываются в регистр) и сохраняются до тех пор, пока значение сигнала на входе G остается равным «0». Пусть адрес порта ввода равен 0A0H (Рис. 4.17а). Такой выбор правомерен, поскольку данный адрес не выходит за пределы области 00H...0FFH. Схема выборки адреса порта, построенная по тому же принципу, что и схема выборки адреса памяти (на Рис. 4.17а не показана), вырабатывает сигнал, принимающий нулевое значение только в том случае, когда значащие цифры восьми младших разрядов адресной шины образуют двоичное число «10100000», что соответствует шестнадцатеричному коду 0A0H. Вызов процессором данного порта ввода происходит, если од-новременно с сигналом обращения процессора к порту подаются сигналы IORQ и RD, значения которых должны быть равны «0». Для проверки условия поступления всех трех сигналов применяется 3-входовая схема «И-НЕ» с тремя инверторами (вентили «НЕ»). В портах ввода вход G обычно соединяют с положительным полю- 0 ... 9 10 11 12 13 14 15 ... 39 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||