Раздел: Документация

0 ... 8 9 10 11 12 13 14 ... 39 подается напряжение от положительного полюса источника питания, что соответствует сигналу «1». В таком случае на выводе 13 сигнал будет равен «О» до тех пор, пока мы не замкнем хотя бы один из выключателей. Тогда, в соответствии с Табл. 4.2, произойдет инверсия сигнала на выходе. Однако работа такой схемы будет неустойчивой, поскольку на свободных входах могут оказаться случайные электрические сигналы (например, помехи от электростатических разрядов), способные на некоторое время изменить напряжение в очень широких пределах. Для обеспечения надежной работы в цепь выводов 12 и 13 необходимо включить резисторы сопротивлением 1...3 кОм (вентиль D). Их роль состоит в том, чтобы надежно зафиксировать на входах вентиля напряжение, соответствующее логической «1» (+5 В). Функциональные возможности интегральных схем ТТЛ можно значительно расширить путем составления различных комбинаций вентилей, соединенных друг с другом. Для этого часто соединяют выход логического элемента с его входом или подключают непосредственно к выходу одного вентиля входы нескольких других вентилей. Максимальное количество входов вентильных схем, которые можно присоединить к одному выходу, называется нагрузочной способностью или коэффициентом разветвления. У стандартного вентиля ТТЛ коэффициент разветвления равен 10. Коэффициент разветвления по выходу, или нагрузочная способность Число схем, которые можно подключить к выходу данной схемы К выходу ТТЛ-схемы можно подключить до 10 ТТЛ-входов Схемы с Z-состоянием Как известно, любая логическая переменная может принимать только два значения, поэтому на выходе логической цифровой схемы, реализующей какую-либо булеву функцию, достаточно двух состояний: состояние «1», соответствующее значению переменной «истинно» и состояние «0», соответствующее значению «ложно». Тем не менее в некоторых случаях, учитывая специфику работы конкретных типов цифровых схем, их наделяют способностью находиться еще и в третьем состоянии, называемом высокоомным, или Z-состоянием. Высокоомное состояние представляет собой состояние разрыва цепи между выходным выводом и внутренней частью интегральной схемы. Как показано на Рис. 4.8, схема находится в высокоомном состоянии на выходе, если на входе ОС присутствует сигнал «1». Эта функция интегральной схемы дает возможность на некоторое время «отключить» ее выход от остальной части электронного устройства. Такой режим работы может понадобиться, например, чтобы снизить потребление энергии от источника питания выходной цепью тех ИС, которые в данный момент не производят никаких операций с данными.

Рис. 4.8. Интегральная схема с Z-состоянием Дешифратор Дешифратор вырабатывает сигнал на том выходе, двоичный адрес которого установлен на его входе. Иначе говоря, дешифратор выполняет функцию устройства идентификации (распознавания) двоичных чисел. На Рис. 4.9 показан 3-разрядный дешифратор (74LS138). Эта интегральная схема имеет три входа для сигналов управления - Gl, G2A и G2B. Сигналы управления синхронизируют работу дешифратора. Как вы уже могли заметить, маленькие кружки на схеме у выводов означают инверсию сигнала. Дешифратор находится в активном состоянии, когда на вывод G1 подается сигнал «1», а на выводы G2A и G2B - «О». Во всех остальных случаях на всех выходах от Y0 до Y7 сигнал соответствует «1». На Рис. 4.9 справа дана таблица соответствия некоторых кодовых комбинаций дешифратора. Если состояние на адресных входах А, В, С представить двоичным числом, то на выходе, номер которого равен значению этого числа, устанавливается «О». Дешифраторы обычно используются для преобразования двоичного числа в десятичное. В процессоре микрокомпьютера он часто играет роль селектора, который через шину адреса выбирает требуемый кристалл устройства памяти или порт ввода-вывода. Подробнее об этом мы расскажем в следующем разделе (4.4). 3-разрядный дешифратор YO Yl Y2 Y3 Y4 Y5 Y6 Пб1П51П41Пз1[2]ГП1ГТ01Г9 . . . . . ГШ Пг1 Ш1 По! ПП ЧА A I A A А Примеры кодов дешифратора 74LS138 га .....ТТ...... ш ш Ш Ш Ш Ш ш В С G2AG2BG1 Y7 IGND

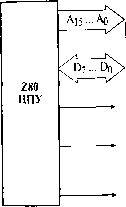

Входные Синхросигналы сигналы (адреса) -/V. Распознаются 3-разрядные двоичные числа СИ?6Гйт,ЖппяРУЮТ Дешифратор работает, только раооту дешифратора когда имеет место СЛедуЮщая комбинация сигналов: G1 = «1», G2A = G2B = «0» Рис. 4.9. Дешифратор (74LS138) 84 ======== Защелка Схема защелки выполняет следующую функцию: она сохраняет (фиксирует) данные в течение некоторого промежутка времени. В микрокомпьютере защелки применяются в портах ввода-вывода или в регистрах различных типов. Защелка представляет собой электронную схему, состоящую из множества вентилей и триггеров. Например, 8-разрядная схема защелки регистра (74LS373) содержит восемь D-триггеров, сформированных на одном кристалле ,(Рис. 4.10). Это ТТЛ-схема с Z-состоянием. Поэтому, как мы уже знаем, если на вывод ОС подать «1», то на всех ее выходах установится высокоомное состояние. Если на вывод G подать сигнал «1», то значения сигналов на входах 1D...8D без изменений передадутся на выходы 1Q...8Q. Это состояние на выходах будет сохраняться до тех пор, пока на вывод G будет подаваться сигнал «О». Именно такая 8-разрядная схема-защелка применяется в портах ввода-вывода микрокомпьютера. 8-разрядная «защелка» 8Q 8D 7D 7Q 6Q 6D 5D 5Q G И[Г91[Г81[Гт1та[ТаИИИГгП 74LS373 (ТТЛ с Z-состоянием); содержит восемь D-триггеров GND шшшшшшшшшм" ОС 1Q ID 2D 2Q 3Q 3D 4D 4Q Входы: 1D ... 8D (8-разрядное число) Выходы: 1Q...8Q Если на вход ОС подать «Ь, то на выходе установится высокоомное состояние Когда на входе G сигнал равен «1», значения сигналов с D-входов передаются на Q-выходы Когда G = «0», выходы сохраняют предыдущее состояние В момент перехода вывода G из состояния «1» в состояние «О» входные данные «защелкиваются» в выходном регистре Рис. 4.10. Схема защелки ТТЛ 4.4. АРХИТЕКТУРА МИКРОКОМПЬЮТЕРА Как уже было отмечено во второй главе, основными компонентами микрокомпьютера являются центральный процессор, состоящий из вычислительного и управляющего блоков, запоминающее устройство, в которое заносятся данные и программа, а также порты ввода-вывода, осуществляющие обмен данными между процессором и внешними устройствами. Теперь рассмотрим, каким образом осуществляется соединение процессора с ЗУ и портами ввода-вывода. На Рис. 4.11 представлен пример простейшей схемы микрокомпьютера, состоящего из процессора Z80, двух БИС, выполняющих функции постоянного запоминающего устройства, двух БИС оперативного запоминающего устройства и одной интегральной схемы, играющей роль портов ввода-вывода. Al5-0 Z80 ЦПУ D7-0 MREQ RD WR IORQ V- Шина адреса A[5... Aq ПЗУ ® ПЗУ ОЗУ © ОЗУ ® v v ИС портов ввода-вывода Шина данных 7- D0 • MREQ RD WR •IORQ Рис. 4.11. Структурная схема микрокомпьютера Соединение процессора и ЗУ Пожалуйста, не поленитесь перелистать книгу немного назад и еще раз взгляните на Рис. 2.4, на котором показаны сигналы про- цессора Z80. Из 40 выводов процессора Z80 к устройствам памяти имеют отношение адресная шина А15...АО (16 выводов) и шина данных D7...D0J8 выводов), а также выводы сигналов управления MREQ , RD, WR. То есть всего получается 27 выводов. Все эти сигналы показаны на Рис. 4.12.  16-разрядная шина адреса Указывает адрес памяти в области от ООООНдо 0FFFFH -разрядная шина данных По шине данных ЦПУ посылает данные в запоминающее устройство и принимает их Сигнал MREQ [ Оповещает о запросе памяти процессором Сигнал RD Устанавливает ЗУ в режим считывания данных процессором Сигнал WR Устанавливает ЗУ в режим записи данных Рис. 4.12. Основные сигналы обмена данными между ЦПУ и ЗУ Давайте в качестве примера рассмотрим 8-разрядное оперативное запоминающее устройство объемом 2 Кбайта, показанное на Рис. 4.13. Адресная шина процессора имеет 16 выводов А15...А0. Следовательно, он может указать 65536 адресов (216), что соответствует 64 К (1 К = 1024 = 210). По шестнадцатеричной системе счисления весь этот диапазон адресов перекрывает область чисел от 0000 Н до 0FFFFH. В то же время объем памяти рассматриваемого нами ОЗУ составляет лишь 2 Кбайта. Поэтому мы должны решить, к каким именно адресам процессора (из 1024) «привязать» эти 2 Кбайта. Например, мы можем назначить ОЗУ, имеющее объем памяти 2 Кбайта, адреса от 8000Н до 87FFH (область С, см. Рис. 4.14). 0 ... 8 9 10 11 12 13 14 ... 39 |

||||||||||||||||||||||||||||||||||||||||||||||||