Раздел: Документация

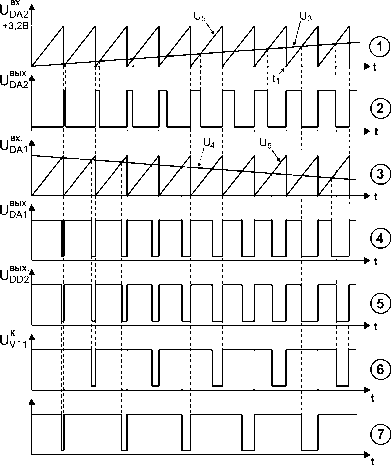

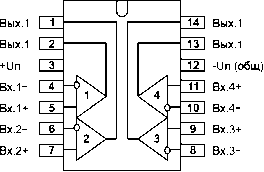

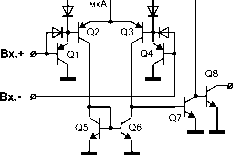

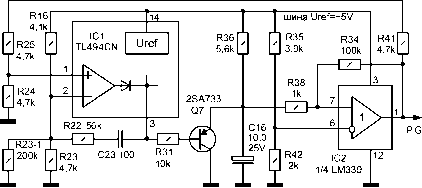

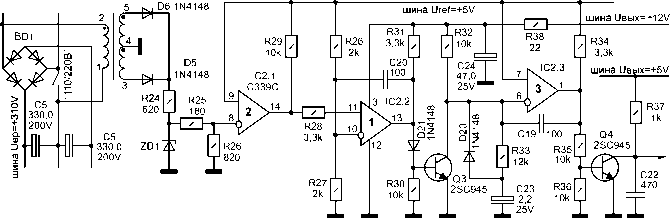

0 ... 14 15 16 17 18 19 20 ... 30  UVT2 Рис. 47. Временные диаграммы, поясняющие процесс плавного (мягкого) запуска ИБП и иллюстрирующие работу управляющей ИМС TL494 в пусковом режиме: U3,U4,U5 - напряжения на выводах ИМС 3, 4 и 5 соответственно. ляется опорное напряжение Uref. Пилообразное выходное напряжение генератора поступает на инвертирующие входы компараторов DA1 и DA2. На инвертирующий вход ШИМ-компаратора DA2 подается выходное напряжение усилителя ошибки DA3. Так как выходные напряжения блока (в том числе и +5В) еще отсутствуют, то сигнал обратной связи, снимаемый с делителя R19, R20 и подаваемый на неинвертирующий вход усилителя ошибки, равен 0. На инвертирующий вход этого усилителя подается некое положительное напряжение, снимаемое с делителя SVR, R24, R22 в цепи шины опорного напряжения Uref, которое уже имеется. Поэтому выходное напряжение усилителя ошибки DA3 будет равно 0 в первоначальный момент, а по мере заряда выходных конденсаторов фильтров - будет нарастать. Выходное напряжение ШИМ-компаратора DA2 по этой причине будет представлять собой нарастающую по ширине последовательность импульсов. Этот процесс отображен на временных диаграммах 1 и 2 (рис.47). Неинвертирующий вход компаратора "мертвой зоны" DA1, подключен к выводу 4 IC1. К этому выводу подключается внешняя RC-цепь С19, R20, которая запитывается с шины опорного напряжения Uref. Поэтому при появлении Uref все оно в первый момент выделяется на резисторе R20, т.к. конденсатор С19 полностью разряжен. По мере заряда С19 ток через него и резистор R20 уменьшается. Поэтому падение напряжения на R20, которое подается на вывод 4 1С 1, имеет форму спадающей экспоненты. В соответствии с этим выходное напряжение компаратора "мертвой зоны" DA1 будет представлять собой последовательность уменьшающихся по ширине импульсов. Этот процесс отображен на временных диаграммах 3 и 4 (рис,47). Таким образом процессы широтного изменения выходных напряжений компараторов DA1 и DA2 имеют взаимно противоположный характер. Выходные напряжения компараторов являются входными для логического элемента DD1 (2-ИЛИ). Поэтому ширина импульса на выходе этого элемента определяется наиболее широким из входных импульсов. Из временной диаграммы 5 (рис. 47), отображающей выходное напряжение DD1, видно, что вплоть до момента ti ширина выходных импульсов компаратора DA1 превышает ширину выходных импульсов ШИМ-компаратора DA2. Поэтому переключения этого компаратора не влияют на ширину выходного импульса DD1, а значит и выходного импульса IC1. Определяющим на интервале to-ti является выходное напряжение компаратора DA1. Ширина выходных импульсов IC1 на этом интервале плавно нарастает, что видно из временных диаграмм 6 и 7 (рис. 47). В момент ti выходной импульс компаратора DA1 сравнивается по ширине с выходным импульсом ШИМ-компаратора DA2. В этот момент происходит передача управления от компаратора DA1 к ШИМ-компаратору DA2, т.к. его выходные импульсы начинают превышать по ширине выходные импульсы компаратора DA1. За время to-ti выходные конденсаторы фильтров успевают плавно зарядиться, и блок успевает выйти в номинальный режим. Таким образом суть схемотехнического решения проблемы "мягкого" запуска заключается в том, что на время зарядки конденсаторов выходных фильтров ШИМ-компаратор DA2 подменяется компаратором DA1, работа которого не зависит от сигнала обратной связи, а определяется специальной формирующей RC-цепочкой C19.R20. Из рассмотренного выше материала следует, что перед каждым включением ИБП конденсатор формирующей RC-цепи (в данном случае С19) должен быть полностью разряжен, иначе "мягкий" запуск будет невозможен, что может привести к выходу из строя силовых транзисторов преобразователя. Поэтому в каждой схеме ИБП предусмотрена специальная цепь для быстрого разряда конденсатора формирующей цепочки при выключении ИБП из сети или при срабатывании токовой защиты. СХЕМА ВЫРАБОТКИ СИГНАЛА PG (POWER GOOD) Сигнал PG, наряду с четырьмя выходными напряжениями питания системного блока, является стандартным выходным параметром ИБП. Наличие этого сигнала является обязательным для любого блока, соответствующего стандарту IBM (а не только блоков, построенных на основе микросхемы TL494). Однако в компьютерах класса XT этот сигнал иногда не используется. В ИБП встречается большое разнообразие вариантов схем выработки сигнала PG. Условно все разнообразие схем можно разделить на две группы: однофункциональные и двухфункциональ-ные. Однофункциональные схемы реализуют только функцию задержки появления разрешающего запуск процессора сигнала PG Н-уровня при включении ИБП. Двухфунациональные схемы, кроме вышеуказанной функции, реализуют еще и функцию упреждающего перехода сигнала PG в неактивный низкий уровень, запрещающий работу процессора при выключении ИБП, а также в случаях возникновения различного рода аварийных ситуаций, прежде чем начнет уменьшаться питающее цифровую часть системного модуля напряжение +5В. Большинство схем выработки сигнала PG являются двухфункциональными, но при этом они являются более сложными, чем схемы первого типа. В качестве базового элемента при построении этих схем широко используется микросхема типа LM339N, представляющая из себя счетверенный компаратор напряжения (рис. 48). Выходные транзисторы каждого компаратора, имеют открытый коллектор (рис. 49). Вывод 12 LM339N подключается к "корпусу", а на вывод 3 заводится однополярное (от +2В до +30В)питание. Благодаря высокой чувствительности компа-раторных схем обеспечивается необходимое быстродействие. Рассмотрим подробнее несколько характерных вариантов построения схем выработки сигнала PG. Схема выработки сигнала PG, использованная в блоке GT-200W, показана на рис. 50. Функция задержки при включении питания реализуется следующим образом. При включении блока в сеть срабатывает схема пуска и на шине Uref появляется опорное напряжение +5,1 В от внутреннего источника микросхемы TL494. Выходное напряжение +5В еще отсутствует. Поэтому делитель обратной связи R25, R24 еще не запитан (потенциал вывода 1 микросхемы равен 0В). Делитель же, дающий опорный уровень на выводе 2 микросхемы, уже запитан напряжением Uref. Поэтому выходное напряжение усилителя ошибки минимально (на выводе 3 потенциал около 0В), а запитанный по коллектору тем же напряжением Uref транзистор Q7 открыт и насыщен током базы, протекающим по цепи: Uref - R36 - э-б Q7 - R31 - внутренние цепи TL494 - "корпус".  Рис. 48. Функциональная схема ИМС LM339 (вид сверху). +Un 0 3,5V мкА О Оз,р о \100 мкА  )100 мкА Вых. Рис. 49. Принципиальная электрическая схема одного компаратора ИМС LM339. шина UBbix=+5V  Рис. 50. Схема образования сигнала PG в ИБП GT-200W. Потенциал неинвертирующего входа компаратора 1 микросхемы IC2 (LM339N) равен 0, и, т.к. на инвертирующем входе его присутствует положительный потенциал с резистора R42 делителя R35, R42 в цепи Uref, сам компаратор будет находиться в состоянии 0В на выходе (выходной транзистор компаратора открыт и насыщен). Поэтому сигнал PG имеет L-уровень и запрещает работу процессора. Далее начинает появляться выходное напряжение +5В по мере зарядки выходных конденсаторов большой емкости. Поэтому выходное напряжение усилителя ошибки DA3 начинает возрастать, а транзистор Q7 закрывается. Вследствие этого начинает заражаться задерживающая емкость С16. Ток зарядки протекает по цепи: Uref -R36-C16-"корпус". Как только напряжение на С16 и на неинвер-тирующем входе компаратора 1 (вывод 7 IC2) достигнет опорного уровня на инвертирующем входе его (вывод 6 IC2), выходной транзистор компаратора закроется. ПОС, которой охвачен компаратор 1 (резистор R34), обуславливает наличие гистерезиса на передаточной характеристике этого компаратора. Этим обеспечивается надежность срабатывания схемы PG и исключается возможность "опрокидывания" компаратора под воздействием случайной импульсной помехи (шума). На шине +5В к этому моменту появляется полное номинальное напряжение» а сигнал PG становится сигналом Н-уровня. Из вышеизложенного видно, что датчиком состояния блока (включен/отключен) в данной схеме является выходное напряжение усилителя ошибки DA3, снимаемое с вывода 3 управляющей микросхемы IC1 (TL494), а схема является одно-функциональной. Более сложная схема выработки сигнала PG реализована в ИБП APPIS (рис. 51). В этой схеме задействованы три компаратора микросхемы IC2. Функция задержки при включении питания реализуется следующим образом. После включения ИБП в сеть и срабатывания схемы пуска появляется опорное напряжение Uref. Выходные напряжения блока еще отсутствуют. Поэтому микросхема IC2 и транзистор Q3 еще не запитаны. Транзистор Q4, с коллектора которого снимается сигнал PG, открыт, т.к. запи-тан его базовый делитель. Ток базы протекает по цепи: Uref- R34 - R35 - б-э Q4 - "корпус". Поэтому PG имеет L-уровень. Кроме того, с шины Uref происходит заряд конденсатора С21 по цепи: Uref- R29 - С21 - "корпус". С появлением выходных напряжений блока с шины +12В через фильтр развязки R38, С24 запи-тываются микросхема IC2 и транзистор Q3. С шины +5В запитывается по коллектору полным напряжением транзистор Q4. При этом происходят следующие процессы. На инвертирующий вход контролирующего компаратора начиная с момента включения блока поступает несглаженное выпрямленное двухпо-лупериодной схемой D5, D6 напряжение со вторичной обмотки 3-4-5 специального трансформатора Т1. Это пульсирующее напряжение с амплитудой около 15В подается на инвертирующий вход компаратора 2 через звено амплитудного ограничения R24, ZD1 (стабилитрон на 11В) и ре- -220В 50Гц зистивный делитель R25, R26. Так как амплитуда импульсов после ограничения и деления все же остается большей, чем уровень опорного напряжения на неинвертирующем входе компаратора 2, то каждым импульсом и почти на все время его действия компаратор 2 переводится в состояние ОВ по выходу (выходной транзистор компаратора будет открыт). Поэтому за несколько импульсов конденсатор задержки С21 разряжается практически до ОВ. Поэтому компаратор 1 переключается по выходу в состояние ОВ, т.к. напряжение на неинвертирующем входе его определяется уровнем напряжения на конденсаторе С21. В результате транзистор Q3 запирается нулевым смещением. Запирание Q3 приводит к зарядке второго задерживающего конденсатора С23 по цепи: +12В - R38 - R32 - R33 - С23 - "корпус". Как только напряжение на коллекторе Q3, а следовательно, и на инвертирующем входе компаратора 3 достигнет порогового уровня на его инвертирующем входе (Uref=+5,1B), компаратор 3 переключится в состояние ОВ на выходе (выходной транзистор компаратора открывается). Поэтому базовый для Q4 делитель R35, R36 окажется незапитанным, и Q4 запрется. Так как на шине +5В уже присутствует полное напряжение, a Q4 заперт, то сигнал PG становится Н-уровия. Функция упреждения при выключении питания реализуется следующим образом. При выключении блока из сети сразу же перестает поступать выпрямленное напряжение со вторичной обмотки 3-4-5 TL и схемы выпрямления D5, D6. Поэтому компаратор 2 сразу переключается, его выходной транзистор закрывается. Далее начинает заряжаться от Uref через R29 емкость задержки С21. Этим предотвращается срабатывание схемы при случайных кратковременных провалах сетевого напряжения. Когда С21 зарядится до половины напряжения Uref, компаратор 1 переключится. Его выходной транзистор закроется. Тогда откроется транзистор Q3 током базы, протекающем по цепи: +12В - R38 - R31 -D21 -б-э Q3-"корпус". Емкость второй задержки С23 быстро разряжается через Q3 и ускоряющий диод D20 по цепи: (+)С23 - D20 - к-э Q3 - "корпус" - (-)С23. Потенциал инвертирующего входа компаратора 3 станет быстро уменьшаться со скоростью разряда С23. Поэтому компаратор 3 переключится, выходной транзистор его закроется, и базовый делитель для Q4 оказывается запитан с шины  P.G. Рис. 51. Схема образования сигнала PG в ИБП "Appis". 0 ... 14 15 16 17 18 19 20 ... 30 |