Раздел: Документация

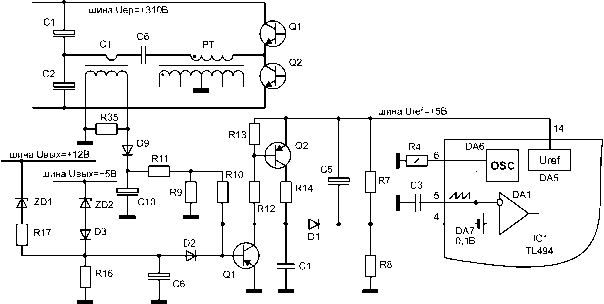

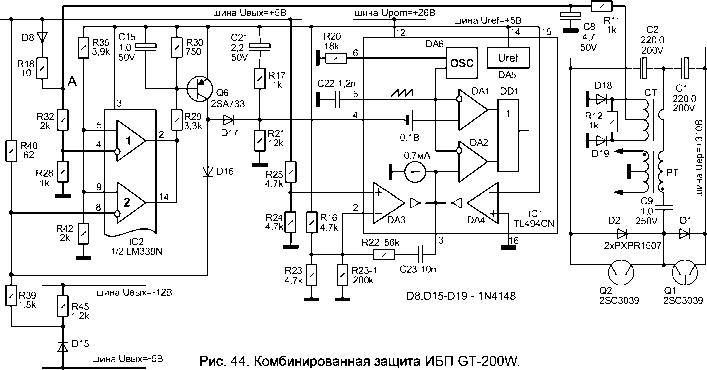

0 ... 11 12 13 14 15 16 17 ... 30  Рис. 43. Комбинированная защита ИБП ESP-1003R (ESAN ELECTRONIC COMPANY, Ltd.). на первичной стороне ИБП (в отличие от предыдущих двух случаев). Этим датчиком является трансформатор тока СТ, первичная обмотка которого включена последовательно с первичной обмоткой силового импульсного трансформатора РТ. Токовые импульсы, протекающие по первичной обмотке СТ, трансформируются во вторичную его обмотку, выпрямляются с помощью мостовой схемы D9-D12 и сглаживаются конденсатором С8. Резистор R14 является нагрузкой вторичной обмотки СТ. Наличие этой нагрузки является обязательным условием нормальной работы СТ. Уровень напряжения на конденсаторе С8 пропорционален ширине токовых импульсов через первичную обмотку СТ (а значит, и ширине управляющих импульсов на базах силовых транзисторов Q1, Q2 инвертора). Это напряжение подается на пороговую схему, собранную на стабилитроне ZD2 и резисторе R13. Пробивное напряжение стабилитрона ZD2 равно 5,1В. В режиме нормального токопотребления, когда ширина управляющих импульсов не превышает допустимую величину, напряжение на конденсаторе С8 не превышает уровень +5,1 В. Поэтому стабилитрон ZD2 закрыт и потенциал базы транзистора, Q4 равен ОВ. Транзистор Q4 закрыт, а поэтому закрыты тиристор SCR и транзистор Q3 бистабильной схемы. Поэтому потенциал вывода 4 управляющей микросхемы определяется номиналами резисторов делителя R5, R6, подключенного к шине Uref. Из схемы видно, что при закрытом транзисторе Q3 потенциал вывода 4 в установившемся режиме составит 0,55В. Переключения компаратора DA1 поэтому не влияют на работу микросхемы. При повышенном токопотребле-нии в нагрузке какого-либо из сильноточных каналов ширина управляющих импульсов возрастает. Поэтому напряжение на конденсаторе С8 повышается. Когда это напряжение превысит уровень +5,1 В, стабилитрон ZD2 "пробивается", и в базу транзистора Q4 течет открывающий его ток по цепи: (+)С8 - ZD2 - б-э Q4-R11 - "корпус". Транзистор Q4 открывается, и в управляющий электрод тиристора SCR течет открывающий его ток по цепи: шина Upom - R12 - к-э Q4 - управляющий переход SCR - "корпус". Тиристор открывается и подключает резистор R10 базового делителя R9, R1Q транзистора Q3 к "корпусу". Это вызывает открывание транзистора Q3 базовым током, протекающем по цепи: шина Uref- 3-6Q3-R10- а-к SCR - "корпус". Транзистор Q3 запитан по эмиттеру напряжением Uref с вывода 14 микросхемы. Поэтому при открывании Q3 это напряжение оказывается приложенным через его малое внутреннее сопротивление к выводу 4 управляющей микросхемы, что вызывает защитное отключение. Схема защиты от КЗ в нагрузке слаботочных каналов в данном ИБП отсутствует. Схема защиты от выходного перенапряжения в канале +5В собрана на элементах ZD1, R11. При превышении напряжением на шине +5В пробивного напряжения стабилитрона ZD1 (5,1В), он "пробивается", и в управляющий электрод тиристора SCR течет ток, открывающий его. Это приводит к открыванию транзистора Q3 и защитному отключению. Механизм ограничения ширины управляющих импульсов здесь не используется. Поэтому традиционно на инвертирующий вход усилителя ошибки DA4 (вывод 15) подается напряжение Uref, а неинвертирующий вход (вывод 16) заземляется. Особо необходимо отметить, что в схеме данного ИБП не используется метод групповой стабилизации выходных напряжений, т.е. дроссель групповой стабилизации на выходе ИБП отсутствует. Стабилизация производится только по двум каналам: +5В и +12В гальваническим способом. Между шинами выходных напряжений +5В и +12В включен резистивный делитель-датчик R15, R8. Потенциал в средней точке этого делителя является контролируемым сигналом и подается на резистивный делитель, состоящий из переменного резистора VR и резистора R7. Поэтому сигнал обратной связи, поступающий на неинвертирующий вход усилителя ошибки DA3, является суммарным, т.к. изменение уровня напряжения на любой из шин +5В, +12В отразится на величине потенциала в средней точке делителя-датчика R15, R8, а значит, и на величине сигнала обратной связи, снимаемого с движка переменного резистора VR на неинвертирующий вход усилителя ошибки DA3. Пример 4. Комбинированная защита ИБП ESP-1003R (рис. 43) включает в себя: •отключающую схему контроля ширины управляющего импульса; •полную схему контроля перенапряжения на выходных шинах сильноточных каналов. Эта схема похожа на схему рис.41. Принцип действия отключающей схемы контроля ширины управляющего импульса тот же, что и ранее, за исключением того, что информация о ширине управляющего импульса получается с первичной стороны ИБП. В качестве датчика традиционно используется трансформатор тока СТ, первичная обмотка которого включена последовательно с первичной обмоткой силового импульсного трансформатора РТ. При протекании через первичную обмотку СТ пилообразных импульсов тока на нагрузке его вторичной обмотки (резистор R35) выделяется знакопеременное прямоугольное импульсное напряжение. Это напряжение выпрямляется однополупериодным выпрямителем D9 и сглаживается конденсатором СЮ. Уровень напряжения на конденсаторе C1Q пропорционален ширине токовых импульсов через первичную обмотку СТ, а значит и ширине управляющих импульсов на базах силовых транзисторов инвертора. Напряжение с конденсатора СЮ подается на рези-стивный делитель R11, R9. Часть этого напряжения снимается с резистора R9 делителя и через резистор R10 подается на базу транзистора Q1, который вместе с транзистором Q2 образует бис-табильную схему, определяющую уровень потенциала на выводе 4 управляющей микросхемы IC1. Пока ширина управляющих импульсов не выходит за расчетный предел, напряжение на конденсаторе СЮ близко к ОВ, и поэтому оба транзистора Q1, Q2 будут закрыты. При возрастании ширины управляющего импульса, например в результате повышенного токопотребления в нагрузке какого-либо из сильноточных каналов, уровень постоянного напряжения на конденсаторе СЮ возрастает. Это приводит к приоткрыванию транзистора Q1 базовым током, протекающим по цепи: (+)С10-R11-R10- б-э Q1 - "корпус"- (-)СЮ. Приоткрывание транзистора Q1 влечет за собой приоткрывание транзистора Q2 базовым током, протекающим по цепи: шина Uref - э-б Q2 -R12-K-3Q1 - "корпус". Приоткрывание транзистора Q2 приводит к еще большему приоткрыванию транзистора Q1, т.к. коллектор транзистора Q2 подключен через резистор R14 к базе транзистора Q1, т.е. между транзисторами имеется положительная обратная связь. Лавинообразный процесс взаимного открывания приводит к очень быстрому достижению обоими транзисторами состояния насыщения. Поэтому напряжение Uref, которым запитан по эмиттеру транзистор Q2, оказывается приложенным к выводу 4 управляющей микросхемы, что приводит к защитному отключению. Схема защиты от КЗ в нагрузке слаботочных каналов в данном ИБП отсутствует, однако имеется полная схема защиты от выходных перенапряжений в сильноточных каналах. Схема защиты от перенапряжения в канале +5В собрана на элементах ZD2, D3, R16. Пока напряжение на шине +5В не превышает "пробивного" напряжения стабилитрона ZD2 (+5,1 В), он заперт. Если этот уровень будет превышен, стабилитрон ZD2 "пробьется", и в базу транзистора Q1 потечет отпирающий его ток по цепи: шина +5В - ZD2 - D3 - D2 - б-э Q1 - "корпус". Это приведет к "опрокидыванию" бистабильной схемы и защитному отключению. Аналогичным образом работает и схема контроля перенапряжения на шине +12В, собранная на элементах ZD1, R17, R16. Диоды D3, D2 - развязывающие. Они предназначены для исключения влияния выходных сигналов всех трех защитных схем друг на друга. Конденсатор С6 устраняет возможность срабатывания защитного отключения при кратковременных случайных превышениях выходными напряжениями номинальных значений (например, в процессе установления после возмущающего воздействия в результате работы схемы стабилизации). Пример 5. Комбинированная защита ИБП GT-20QW (рис. 44) включает в себя: •отключающую схему контроля ширины управляющего импульса; •неполную схему контроля КЗ в нагрузке; •неполную схему контроля выходного перенапряжения. Комбинированная защита в этой схеме построена с использованием двух компараторов микросхемы IC2 (типа LM339N). Компаратор 1 является элементом схемы контроля ширины управляющего импульса. Компаратор 2 совмещает функции элемента схемы контроля перенапряжения на шине +5В и элемента схемы зашиты от КЗ в нагрузке слаботочных каналов. Выходы обоих компараторов объединены и воздействуют на состояние пороговой схемы на транзисторе Q6 по логике "ИЛИ". Открывание выходного транзистора любого из компараторов 1, 2 влечет за собой открывание транзистора Q6 и появление напряжения Uref на выводе 4 управляющей микросхемы IC1, а значит и защитное отключение. Схема контроля ширины управляющего импульса выполнена как отключающая. Датчиком ширины управляющего импульса является трансформатор тока СТ, R12 - нагрузка вторичной обмотки СТ. Переменное прямоугольное импульсное напряжение с резистора R12 выпрямляется по двухполупериод-ной схеме со средней точкой (диоды D18, D19). С8 - сглаживающая емкость фильтра. R11 - гасящий амплитуду переменного напряжения резистор. Уровень напряжения на конденсаторе С8 пропорционален ширине управляющих импульсов. Это напряжение подается в точку А делителя D8, R18, R32, R28 и влияет на распределение потенциалов в узлах этого делителя. Напряжение с резистора R28 подается на инвертирующий вход компаратора 1 микросхемы IC2. На неинверти-рующий вход этого компаратора подается опорный уровень с резистора R42 делителя R35, R42, подключенного к шине Uref. Номиналы резисторов  обоих делителей подобраны такими, что пока ширина управляющих импульсов не выходит за диапазон стабилизации, потенциал неинвертирующего входа компаратора 1 (вывод 5) превышает потенциал его инвертирующего входа (вывод 4). Поэтому выходной транзистор компаратора 1 закрыт. При повышенном токопотреблении в нагрузке какого-либо из сильноточных каналов ширина управляющих импульсов начинает возрастать. Поэтому возрастает уровень напряжения на конденсаторе С8, а следовательно, и на инвертирующем входе компаратора 1. Когда потенциал инвертирующего входа превысит потенциал неинвертирующего входа, компаратор 1 "опрокинется", выходной транзистор его откроется. В результате этого резистор R29 базового делителя R30, R29 транзистора Q6 окажется подключен к "корпусу". Поэтому появится путь для протекания отпирающего базового тока транзистора Q6: шина Uref -э-б Q6 - R29 - к-э выходного транзистора компаратора 1 - "корпус". Транзистор Q6 откроется, и напряжение Uref, которым запитан по эмиттеру этот транзистор, окажется приложенным к выводу 4 управляющей микросхемы IC1 через диод развязки D17. Это, как было показано ранее, приведет к защитному отключению. Схема защиты от КЗ в нагрузке слаботочных каналов имеет датчиком традиционный делитель D15, R45, подключенный между шинами выходных напряжений -5В, -12В. При номинальных уровнях напряжений на этих шинах потенциал в средней точке этого делителя составляет около -5,8В. Поэтому резистивный делитель R40, R39 запитывается двуполярно (выходным напряжением +5В и потенциалом -5,8В со средней точки делителя R45, D15). Напряжение со средней точки делителя R40, R39 подается на инвертирующий вход компаратора 2 микросхемы IC2 (вывод 8). Номиналы резисторов делителя R40, R39 подобраны такими, что потенциал инвертирующего входа компаратора 2 (вывод 8) в номинальном режиме меньше, чем потенциал неинвертирую- щего входа (вывод 9), на который подан опорный уровень со средней точки делителя R35, R42, подключенного к шине Uref. При КЗ в нагрузке любого из каналов -5В, -12В потенциал средней точки делителя R45, D15 повышается, и поэтому потенциал инвертирующего входа компаратора 2 начинает превышать потенциал его неинвертирующего входа. Поэтому компаратор 2 "опрокидывается", выходной транзистор его открывается и появляется путь для протекания открывающего транзистор Q6 базового тока: шина Uref - э-б Q6 - R29 - к-э выходного транзистора компаратора 2 - "корпус". Транзистор Q6 открывается, и напряжение Uref с его эмиттера поступает на вывод 4 управляющей микросхемы через диод D17, что влечет за собой защитное отключение. Для ускорения "опрокидывания" система, состоящая из компаратора 2 и транзистора Q6, охвачена положительной обратной связью с помощью диода D16. Контроль за выходным перенапряжением на шине +5В осуществляется с помощью цепочки D8, R18. При превышении напряжением на шине +5В расчетного уровня (около +5,1 В) соотношение между потенциалами инвертирующего и неинвертирующего входа компаратора 1 микросхемы IC2 изменяется на противоположное. Компаратор "опрокидывается", выходной транзистор его открывается, открывается транзистор Q6, и напряжение Uref с его эмиттера поступает на вывод 4 управляющей микросхемы, что влечет за собой защитное отключение. Механизм ограничения ширины управляющего импульса здесь не используется. Поэтому усилитель ошибки DA4 исключается из работы микросхемы традиционным способом: на инвертирующий вход (вывод 15) подано напряжение Uref, а неинвертирующий вход (вывод 16) заземлен. Следовательно, выходное напряжение усилителя DA4 независимо от режима, в котором находится схема ИБП, всегда равно ОВ и не влияет на работу управляющей микросхемы IC1. 0 ... 11 12 13 14 15 16 17 ... 30 |