Раздел: Документация

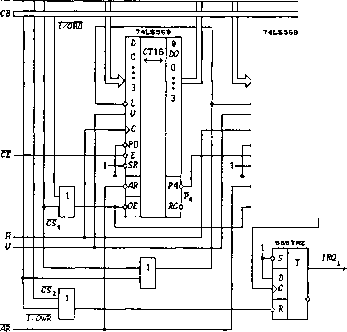

0 ... 111 112 113 114 115 116 117 ... 119 чика сигнал 777 Ps = U П Qr v 77 • Y[Qr = 77- Y[QT = Р77, r=0r=0г=0 где Pg = 1 в нулевом состоянии счетчика, Р8 - сигнал заема. Работа триггера знака числа N описывается функцией переходов Q+ = x-dPjH~\/QsdP7H, поэтому при достижении нулевого состояния сигнал заема Ps - 1, а значит Q\ = х при dH - 1 и U = ж ф Q5 = 1, что обеспечивает переход в следующем такте из состояния j = 0 в состояние j = 1 независимо от значения х при знаке Qs числа N, равном текущему значению х. На рис. 7.87,в изображены временные диаграммы, построенные на основании приведенных выше функций, - длительность импульсного сигнала а = dPsH определяется быстродействием используемых ИС и составляет 50 ... 100 не при построении схемы на ИС серии 555. Из этого следует, что схема счета в прямом коде представляет собой асинхронный импульсный автомат. Быстродействие таких автоматов значительно ниже быстродействия синхронных автоматов, так как они срабатывают и от входных информационных сигналов (в данном случае от сигнала х) между двумя соседними воздействиями импульсного сигнала dH = 1. Сигнал CLR (Clem--очистка) служит для синхронного сброса счетчика в нулевое состояние. В описанной схеме можно использовать и двоично-десятичные реверсивные счетчики. Пример применения реверсивных счетчиков в микроконтроллерах и микроЭВМ приведен на рис. 7.88. Структура системных шин показана для случая использования микропроцессора 580ВМ80 (DB - Data Bus, А В - Address Bus, СВ -Control Bus, 1/RD - I/O Read, I/OWR - I/O Write, CSk - Chip Select). Программируется модуль пересчета загрузкой в счетчик 8-разрядного двоичного числа d\j сигналом I/OWR при значении адресного сигнала С Si = 0, выдаваемого дешифратором портов внешних устройств. Поскольку загрузка синхронная, то длительность значения сигнала загрузки L = I/OWR - СSi = 0 должна быть больше периода тактового сигнала Н. Чтение состояния счетчика производится по шине данных DB сигналом ОЕ = I/ORD • С Si при выполнении команд ввода 8-dtt System Data Bus ZE

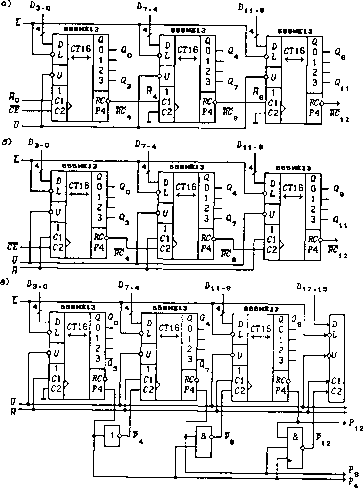

Рис. 7.88 программы обслуживания внешнего устройства, выполняемой микропроцессором. При переполнении счетчика устанавливается значение сигнала IRQi = 1 (Interrupt Request - запрос прерывания), который подается на контроллер прерываний для организации ввода-вывода по прерыванию. После обслуживания прерывания производится загрузка числа d\f и сброс триггера запроса прерывания сигналом R = I/OWR • С 5г. Формировать сигналы AR, U и СЕ можно как аппаратно, так и программно. При программном формировании сигналов U и СЕ требуется добавить два триггера (одну ИС 555ТМ2), управление которыми производится подобно управлению триггером, формирующим сигнал IRQi (только следует задать D = DB0 для установки значений сигналов 0 и 1, задаваемых программным способом по шине данных). Каскадирование счетчиков типа 555ИЕ13. Методы каскадирования счетчиков с сигналами переполнения (7.52) и (7.54) отличаются от ранее рассмотренных методов. Реверсивный счетчик имеет два сигнала переполнения (см. рис. 7.77) P4 = U- q3q2q1q0 V U QzQiQxQo иЁС = СЕР4Н, один из которых описывается функцией (7.54). Сигнал RC стро-бируется тактовым сигналом Н, поэтому он принципиально не может иметь ложных значений во время переходных процессов. Значит, этот сигнал можно подать на тактовый вход Н другого счетчика. В результате будет получен асинхронный импульсный счетчик (рис. 7.89,а), описываемый функциями: fc-ifc-i Hk = RCk = СЕ (U Qr V 77- П Qr) Но, (7.60) г=0r=0 где k - 4,8,12. Максимальное значение частоты тактового сигнала Но не зависит от числа каскадов. Схема синхронного счетчика с последовательным переносом изображена на рис. 7.89,5. Она построена по тому же принципу, что и схема, показанная на рис. 7.86,а. Легко показать, что сигналы переполнения RCk описываются функциями: fc-ifc-i RCk = CE-H .(U Y[Qr V77- Y[Qr), fc = 4,8,12, (7.61) r=0r-0 которые отличаются от функций (7.58) только стробированием тактовым сигналом Н. Поскольку длительность активного уровня сигнала RC4 вдвое меньше, чем у сигнала переполнения Р4 (см. рис. 7.78), то задержка сигнала RC4 в последовательно соединенных счетчиках не должна превышать полпериода тактового сигнала Н (допустимая задержка вдвое меньше, чем в схеме, приведенной на рис. 7.86,а, при равенстве полупериодов тактового сигнала Н). Чем выше порядок КС, реализующей функции переноса (7.61), тем меньше максимальное значение частоты тактового сигнала. Схему синхронного счетчика с параллельным переносом можно построить только при использовании внешних ЛЭ (рис. 7.89,е) для формирования сигналов разрешения счета fc-i Pk = U l\QryUl\Qr,(7.62) r=0r=0 где k = 4,8,12, которые совпадают с функциями (7.58) при значении сигнала СЕ - 1. Для реализации функций (7.62) требуются многовходовые ЛЭ И-НЕ.  Рис. 7.89 Каскадирование счетчиков с одним сигналом управления Р0. Счетчики с таким сигналом управления и функцией переполнения (7.52) изготавливаются по КМОП-технологии: например, ИС 561ИЕ11 (см. рис. 7.74) и 561ИЕ14 (см. рис. 7.83). Структурная схема 20-разрядного асинхронного импульсного двоичного реверсивного счетчика изображена на рис. 7.90,а: (ОD3.0 <3Э 0 D7.4 07.411-8 О-и-е 13-1 2 Gl5-12D,9 16 Q19- 44. 5-I CT16 U R U- T CT16 Q -1 i/ r X CT16 Я -r-iPO P4A-•fAbPD P4A-ApD P4t Лю Р4б--4ЦрО Р46-» i/ r CT16 У r I 4. D L CT16 U R T BSlUIllШИШSS1HE11В81ИЖ11ШИШ °">D3.0 Q3.0 d7.4 Q7-4D11-8 Oll-e D1S-12 Gl5-12D19-16 Ql9-16 CT- i CT16 -f>c U R 4. • 4. • D L CT16 Q -1 У r 3X CT16Q PO P4A 6P0 P46-APO P4A-6P0 P4i--APD P46-+ hC U R Р,2Г>С CT16 Q-> U R P r->C 18 K CT16 C i/ r В61ИЖ11SSlKEllBSlMIllBSlUIllBS1HI11 Рис. 7.90 fc-1fc-1 Hk = Pk = H0U HQrVHoU- П Or.(7-63) r=0r=0 где = 4,8,12,16,20. Данные функции совпадают с функциями (7.60) при значении сигнала СЕ = 1. Максимальное значение частоты тактового сигнала Я о не зависит от числа каскадов. Схема 20-разрядного синхронного счетчика с последовательным переносом изображена на рис. 7.90,6. Легко показать, что сигналы переполнения Рк описываются функциями k-i k-i Pk = CE-U -JlQrVCE-U l[Qr, k = 4,8,12,16,20, (7.64) r=0r=0 которые совпадают с функциями (7.58). Задержка сигналов Pk должна быть меньше периода тактового сигнала Н. Схему счетчика с параллельным переносом выполнить невозможно даже при использовании внешних ЛЭ при функции переноса типа (7.52). Генератор параллельного переноса для счетчиков. Принцип построения схемы параллельного переноса на ЛЭ И-НЕ был рассмотрен на примере счетчика, изображенного на рис. 7.89,в. Выпускается универсальный генератор параллельного (ускоренного) переноса 74Л5264 (рис. 7.91,a; CLA - Look-Ahead Carry Generators for Counters). Данный генератор описывается функциями: рх - AqBq V AqCE, р2 = аХВХ V аха0В0 V аха0се, р3 = а2В2 V а2аХВХ V а2аха0В0 V а2аха0се, ра = А3В3 V а3а2В2 V а3а2аХВХ V а3а2аха0се, рв = В3 V В2 V Вх V В0 V се. ay 4S264 чз,4 2

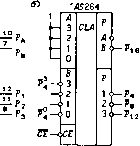

4S264

Рис. 7.91 При подстановке значений сигналов А{ = 1 получаются функции Рх = В0СЁ~, Р2 = ВХВ0СЁ~, Рз = В2ВХВ0СЁ~, РА = В3В2ВХСЁ~, Рв = ВзВ2ВхВ0СЁ, которые представляют собой функции переполнения 4-каскад-ных счетчиков, построенных, например, на 4-разрядных счетчиках с инверсными сигналами Ро и Р4 (рис. 7.91,6). Структурная схема 4-каскадного 16-разрядного двоичного реверсивного счетчика, построенная на основе генератора параллельного переноса, приведена на рис. 7.92. В этой схеме можно использовать и двоично-десятичные счетчики, например, 531ИЕ16. При подстановке значении сигналов В{ = 0 получаются функции Pi = AqCE, Р2 = АХА0СЕ, Р3 = А2АХА0СЕ, Ра = А3А2АХА0СЕ, Рв = СЕ, 0 ... 111 112 113 114 115 116 117 ... 119 |