Раздел: Документация

0 ... 114 115 116 117 118 119 Ш. 1>7-4 Э яг

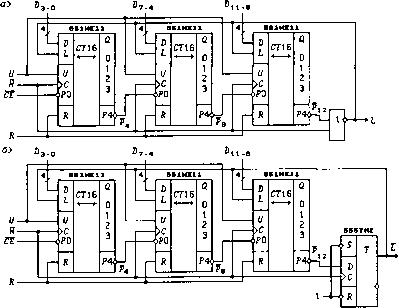

53 от 6 Р4 57. Рис. 7.103 4У ОТ 6 4L И, .п. 1 сг от 6 В7Л:

П. 1 Hci сг от 6 ксф- Р4 0- 1- 2 3 4 «11 14 (7.81) ность его работы ниже надежности работы 4-разрядного счетчика из-за возможного различия в быстродействии ИС, что более вероятно, чем значительное различие быстродействия триггеров внутри ИС. Модули пересчета этого счетчика определяются выражениями: MD = dM,2<dM< 2™ - 1,1 Ми = 2m - 1 - dM = dM, 0 < dM < 2m - 2, J 1 j где m = 12, с?д/ = Du .. Непрограммируемый 12-разрядный двоичный реверсивный счетчик с последовательным переносом и квазисинхронной загрузкой данных приведен на рис. 7.104,а. Надежность его работы гарантирована, так как длительность активного уровня сигнала загрузки L равна периоду тактового сигнала Н. Модули пересчета этого счетчика определяются выражениями: MD = dM + 2, 1 < dM2m - 1, Ми = 2т + 1 - dM = «W + 2, 0 < dM < 2т - 2, где т = 12, d\f - Du .. .D\Непрограммируемый 12-разрядный двоичный реверсивный счетчик с последовательным переносом и квазисинхронной загрузкой данных, выполненной на основе УСВП, приведен на рис. 7.104,6". Модули пересчета этого счетчика определяются выражениями: Md = dM + 3, 0 < dM < 2m - 1, М - 2m 1, если 0 < dM < 2т~1 - 1, М + 2т~х, если 2m 1 < dM < 2m - 1, где т = 12, dM = Du ...DxD0, M - 2m - dM + 2. Реверсивные счетчики 561ИЕ11 и 561ИЕ14 с асинхронной потенциальной загрузкой данных (см. рис. 7.74 и 7.83), изготовляемые по КМОП-технологии, хотя и отличаются по принципу управления от счетчика 555ИЕ13, однако допускают использовать те же методы программирования модуля пересчета. Программируемый 12-разрядный двоичный реверсивный счетчик с последовательным переносом и асинхронной потенциальной загрузкой данных, выполненный на ИС 561ИЕ11 и эквивалентный счетчику, приведенному на рис. 7.103, изображен на рис. 7.105,а. Сигнал загрузки L = P\2H = RC\2, поэтому модули пересчета этого счетчика определяются выражениями (7.80). Программируемый 12-разрядный двоичный реверсивный счетчик с последовательным переносом и квазисинхронной загрузкой данных, выполненный на ИС*561ИЕ11 и эквивалентный 45- Ми = (7.82)  Рис. 7.105 счетчику, приведенному на рис. 7.104,а, показан на рис. 7.105,6. Модули пересчета этого счетчика определяются соотношениями (7.81). В схемах, изображенных на рис. 7.105, можно использовать и ИС 561ИЕ14 при замене сигнала сброса R на сигнал ML управления двоичным/двоично-десятичным счетом. Схема 12-разрядного двоичного счетчика, приведенная на рис. 7.105,6, работает на частоте /тах = 1,6 МГц при напряжении питания Vdd = +5 В. Частота /тах = 2,2 МГц у 4-разрядного двоичного счетчика с квазисинхронной загрузкой (одна ИС 56ШЕИ и D-триггер 561ТМ2; напряжение питания Vdd = +5 В). Программирование модуля пересчета счетчиков с синхронной загрузкой данных и конвейерным переносом. Конвейерный перенос можно использовать не только для организации квазисинхронной загрузки, но и в счетчиках с синхронной загрузкой чисел d\f для увеличения их быстродействия при программировании модуля пересчета. На рис. 7.106 показан программируемый счетчик с конвейерным переносом, выполненный на ИС серии 531. Среднее время задержки распространения от входа тактового сигнала до некоторого выхода ИС tpd характеризует быстродействие схе- мы, в которой сигнал с данного выхода подается по цепи обратной связи на какой-либо управляющий вход схемы. Так, время задержки распространения tpd < 28 не от входа Н до ВЫХОДа Р4 и tpd < 12 нс от вхо-взмит

да В до выхода Q [29]. Из этого следует, что быстродействие счетчика будет примерно в два раза больше при использовании сигнала синхронной загрузки L = Р4, чем при L = Pj. Задержка же сигнала 1 загрузки L на целое число тактов (в данном случае на один) учитывается при вычислении загружаемого числа е?д/ = D3D2D\Dq по заданному значению модуля пересчета Md- Временные диаграммы, изображенные на рис. 7.107,а, поясняют работу счетчика при загрузке числа d\f = 4 - загрузка производится в состоянии счетчика j = 15, т. е. на один такт позже, чем в счетчике, приведенном на рис. 7.94,а. Из графа переходов (рис. 7.107,6) следует, что модуль пересчета Md = 6. В общем случае модуль пересчета определяется выражениями: Рис. 7.106 MD = dM + 2, Мц = 17 - dM,(7.83) где dM = DzD2DiD0, 0 < dM < 15, 2 < MD, Mv < 17. При значении модуля пересчета, равном 17, одно из внутренних состояний j = 15 при U = 0 или j = 0 при U = 1 повторяется дважды за цикл пересчета (рис. 7.108). Время задержки распространения tpd < 15 не от входа Н до выходов Qr в ИС 531ИЕ17 [29], поэтому увеличения быстродействия или надежности работы счетчика можно добиться использованием УСВП (рис. 7.109). Модули пересчета Md и Мц такого счетчика определяются соотношениями (7.79). Схема 4-разрядного двоичного реверсивного счетчика с конвейерным переносом показана на рис. 7.110,а, а его условное графическое изображение - на рис. 7.110,6 (СТРС - Counter with Pipeline Carry). Такие счетчики можно каскадировать всеми рассмотренными ранее методами. На рис. 7.111,а представлена структурная схема 16-разрядного двоичного реверсивного счетчика с последовательным конвейерным переносом и программируемым модулем пересчета. Модули пересчета этого Таблица 7.10. Программирование модуля пересчета

D be Рис. 7.114 Переключение модулей пересчета реверсивных счетчиков. Проектирование счетчиков с переключаемым модулем пересчета может быть выполнено на любом реверсивном счетчике на основании соотношений (7.65) - (7.85), определяющих их модули пересчета. Пусть требуется синтезировать счетчик с четырьмя модулями пересчета, задаваемыми табл. 7.10. Для достижения максимального быстродействия следует использовать счетчик с конвейерным переносом (рис. 7.106), модуль пересчета которого описывается соотношениями (7.83). При включении счетчика на вычитание модуль пересчета Md = d\f + 2, а значит должны загружаться числа d\{ = Md - 2. Занеся эти числа в табл. 7.10, легко найти, что D3 = D0 = 1, D2 = х2, Dx =ii. Полученным функциям соответствует схема, изображенная на рис. 7.114. 7.8. Счетчики с расщепленным тактовым сигналом Тактовый сигнал реверсивных счетчиков С можно представить в виде дизъюнкции двух сигналов: C = (UvU)-C = CuVCD,. где С (Clock) - тактовый сигнал, Си - U - С, Cd - U - С (U - Up - сложение, D - Down - вычитание; при работе счетчика должно выполняться условие Си • Cd = 0). При таком представлении тактового сигнала счетчик должен иметь два входа для подачи двух тактовых сигналов Си и Cd- Для реализации на Т-триггерах операции 4-разрядного счета их функции возбуждения Тт (7.51) после стробирования сигналом С (С Тг) можно подать на динамический вход, предназначенный для подключения тактового сигнала (вход i тригге- ров при этом не используется). Тактовые сигналы Ст триггеров после такого преобразования могут быть представлены в виде: г-1 г-1 Со = С = Си V Со, Ст = Си • П Qi v Cd • П Qj> r = !>2>3- i=oj=o Функция переполнения счетчика P4 (7.51) при этом также должна быть представлена двумя сигналами, получаемыми с помощью стробирования тактовым сигналом С = Crj V Cd- зз Pu = Cu-Jl Qr, Pd = CD П Qr, r=0 где Pu - перенос, Pd - заем. 555HE7,CD40193B 4 2 D -Щ з Г 11 ?u -1>CU СП 6 1 2 з H-a. r=0 555HE6,CS40192B AC\ 1192, AC\ 1193 ССП 6) з ->c</ - >CD СП0 1 2 3 U- [l 2 PD >CU >CD СП0 1 2 3 p- l о e - GND, is Б - GND, is - ucc 4-7 - GND,is, is Рис. 7.115 Счетчики с асинхронной потенциальной загрузкой данных. Реверсивные счетчики, изготавливаемые в интегральном исполнении, имеют входы асинхронной потенциальной параллельной загрузки данных и установки состояния 0. На рис. 7.115 приведены реверсивные счетчики: 555ИЕ7, С Я40193Я, 74ЛС11193 - 4-разрядный двоичный счетчик с асинхронными потенциальными входами R сброса и параллельной загрузки L данных d\f = D3D2D\ DQ (L = 0 - загрузка, L = 1 - счет); 555ИЕ6, СН40192Б, 74 AC I1192 - двоично- десятичный счетчик с асинхронными потенциальными входами R сброса и параллельной загрузки L данных dm = D3D2D\D0 (L = 0 - загрузка, L = 1 - счет). В этих счетчиках вход R имеет приоритет по отношению ко входу загрузки L. Двоично-десятичный реверсивный счетчик с 0 ... 114 115 116 117 118 119 |