Раздел: Документация

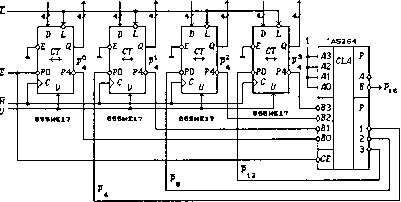

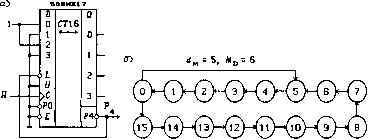

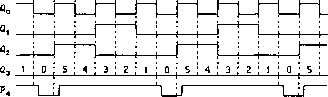

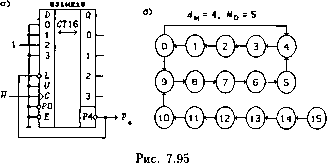

0 ... 112 113 114 115 116 117 118 119 »з-о Q3-0 » 7-4 «7-4 »11-е «4i-e »1з-12 «\  Рис. 7.92 "3-0 «3-0 «3-0 *>7-4 «7-4 *>11-8 «1.-8 *>13-12 «1 D £. £ Q -I 1- £ Q -1 1- Е Q -> СТ <-> РО Р4 -и л СТ Р РО Р4(-Г 1>с > D L СТ <-> РО Р41-Т D L £CTQ РО Р41-, >с Я Чдз дг Д1 до I- вз - вг -в\ -во ct CLA 3 -, которые представляют собой функции переполнения 4-каскад-ных счетчиков, построенных, например, на 4-разрядных счетчиках с прямыми сигналами Ро и Р4 (рис. 7.91,в). Структурная схема 4-каскадного 16-разрядного двоичного суммирующего счетчика, построенная на основе генератора параллельного переноса, приведена на рис. 7.93. В этой схеме можно использовать и двоично-десятичные счетчики, например, 555ИЕ9. Программирование модуля пересчета счетчиков с синхронной загрузкой данных. Методы программирования модуля пересчета не зависят от направления счета, поэтому в любой схеме программируемого двоичного суммирующего счетчика можно использовать и соответствующие по набору управляющих сигналов реверсивные как двоичные, так и двоично-десятичные счетчики (конечно, в схеме следует произвести некоторые изменения, вызванные необходимостью замены сигнала сброса R на сигнал управления направлением счета U и несовпадением активных уровней некоторых сигналов). В частности, все формулы, определяющие модуль пересчета М суммирующих двоичных и двоично-десятичных счетчиков будут справедливы и для соответствующих реверсивных счетчиков при включении их на сложение (U - 1). Значит, остается получить лишь формулы для модуля пересчета тех же схем, но при включении реверсивных счетчиков на вычитание (U = 0). На рис. 7.94,а показана схема включения реверсивного двоичного счетчика на вычитание с программированием модуля пересчета (ср. с рис. 7.54) загрузкой числа йм = DDDxDq = 5 сигналом L = Р4. Как следует из выражения (7.53), сигнал переполнения Р4 = QzQiQiQo - Ко, т-е- сигнал загрузки L = О в состоянии счетчика j = 0, а значит счетчик описывается графом переходов, изображенным на рис. 7.94,6. Из графа переходов видно, что модуль пересчета Мд = 6. Таким образом, в общем случае модуль пересчета MD = dM + 1, dM ф 0; MV = 24 - dM, dM ф 15, (7.65) где Мд - модуль пересчета при значении сигнала U = 0 (вычитание) и допустимых значениях числа d = 1,2,..., 15; Мц - модуль пересчета при значении сигнала U = 1 (сложение) и допустимых значениях числа d = 0,1,..., 14. По заданному модулю пересчета можно найти число d\f = D3D2DiDQ, которое необходимо загружать при каждом переполнении счетчика. Так, из выражения (7.65) следует, что f Md - 1, Md - 2,3,..., 16,..... aM = \ 2*-Mu, Ma = 2,3,...,16.V™>  в) « jnjn riJiJi rij-JiJi  Рис. 7.94 При программировании модуля пересчета реверсивных счетчиков предпочитают включать их на вычитание из-за более естественной работы счетчика (декремент состояний счетчика от значения jmax = йд/ до значения j = 0) и простоты отыскания значений разрядов Dr числа cLm = D3D2D1D0. Временные диаграммы, изображенные на рис. 7.94,в, поясняют работу вычитающего счетчика при загрузке сигналом L числа d\f = 5. На рис. 7.95,а показана схема включения двоично-десятичного реверсивного счетчика на вычитание с программированием модуля пересчета загрузкой числа d\f = D3D2D1D0 = 4 сигналом L = Р4. Как следует из выражения (7.57), сигнал переполнения Р4 = q3q2q1q0 = Ао, т.е. сигнал загрузки L = 0 в состоянии счетчика j = 0. Счетчик описывается графом переходов, изображенным на рис. 7.95,6". Этот граф переходов получен заданием значения U = 0 в полном графе переходов двоично-десятичного счетчика, приведенном на рис. 7.84. Из графа переходов видно, что модуль пересчета Мд = 5. Таким образом, в общем случае модуль пересчета MD = dM + 1, dM ф 0; Мц = 10 - dM, dM ф 9, (7.67) где Mq - модуль пересчета при значении сигнала U = 0 (вычитание) и допустимых значениях числа dM = 1,2, ...,15; Мц  сО 4-0 0°з.о 4-о С 4-о «з-о 4-о «з-о д"* ст1° d3-0 q3-O d7-4 q7-4Dll-e Qll-в D13-12 01s.12 для ct16 ft tT- D L po Q ct >c p-6pq Q CT E P46-*--ae p4a ->c rf D L p0 Q ct 4e р4ф- rt D I po Q ct Ae p4a 1 ) p К у "3-0 u3-0 D3-0 63-0 4-o O3-0 4-0 O3-0 O7- D L po Q ct >c -< -0 Q3-0 ДЛЯ CT10 iJt-4 "n-e Oii-eD,5.12 015.,j для CT16 D L 4po a CT D L CT Oi P49-">C „ CT <-> •6Е P4<v >C r 4-o q3-0 4-o q3-0 Dl-o Ol-o 4-o Q*-o для ct10 d3-0 q3-0 d7-4 Qi-Aii-e Qn-e D1S-12 Q15 12 для ct16 it cT- D L po Q CT ► e p4a- >c 4. Йе 1 >c „ D 2. apo Q CT *-► >e p4a- D L CT 6e p4a-->c ,, D L чро a CT 6E p4a-1-► I К и IP- T - модуль пересчета при значении сигнала U - 1 (сложение) и допустимых значениях числа = 0,1,..., 8, определяемый выражением (7.45). Из выражения (7.67) следует, что dM Г MD-1, MD = 2,3,...,16, I 10-Ми, Ми = 2,3,...,10.1 Для программирования модуля пересчета многокаскадных двоичных счетчиков используется, как правило, сигнал загрузки L = f(Pk)- На рис. 7.96,а показана структурная схема многокаскадного реверсивного счетчика с последовательным переносом и сигналом загрузки L = Pie- Как следует из соотношений (7.53), (7.57) и (7.58) при значениях управляющих сигналов CE=luU = 0, сигнал загрузки L = Pie = Ко, как для двоичных, так и для двоично-десятичных реверсивных счетчиков (К0 = Qi5 • • -QiQo)- Поэтому формулы для модулей пересчета получаются из соотношений (7.65) и (7.67) для 4-разрядных счетчиков простым изменением разрядности чисел. Так, для 16-разрядного двоичного реверсивного счетчика модули пересчета Md = dM + 1, dM ф 0,1 Мц = 2m - dM = d~M + 1, dM ф 2т - 1, J[ где га = 16 - число разрядов счетчика, (1м j= Z>i5.. -DiDq - 16-разрядное двоичное число, dM = Di5 - - D\Dq, Md - модуль пересчета вычитающего счетчика при допустимых значениях числа 6 < dM < 2т - 1, Ми - модуль пересчета суммирующего счетчика при допустимых значениях 0 < dM < 2m - 2. А для 4-разрядного двоично-десятичного реверсивного счетчика модули пересчета Г MD = dM + 1, dM ф 0,,. {ми = 10--аммфЮ--1, «"=Х>--10> (77°) где dM = DlDlDlDlDlDlDlDl.D\D\D\Dl.DlD02D°Dl, т = 4 - число десятичных разрядов счетчика, Md - модуль пересчета вычитающего счетчика при допустимых значениях разрядов 0 < dMi = D3D2D[D0 < 15 и чисел 1 < dM < 15 • (Ю4 - 1)/9 = 16665 (г - номер разряда), Мц - модуль пересчета суммирующего счетчика при допустимых значениях разрядов 0 < djv/i = D3D2D\D0 < 9 и чисел 0 < dM < Ют - 2. При использовании значений разрядов djv/t > Ю счет производится не в десятичной системе счисления с представлением результата счета в коде 8-4-2-1. При использовании счетчиков в качестве делителей частоты это позволяет получать коэффициенты деления MD > 10m - 1. Из выражений (7.69) и (7.70) следует, что для двоичных реверсивных счетчиков загружаемое при программировании число f MD-1, MD = 2,3,...,2m, М \ 2m-Mu = Mu + l, My = 2,3,...,2m,UJl) а для двоично-десятичных загружаемое число d„-l M°~h МД = 2>3,--.,(15-НГ-6)/9, dM-\ i0™-My, Mt/ = 2,3,...,10m(7-72) (например, при m = 4 модули пересчета 2 < Md < 16666). Пример. Пусть требуется спроектировать делитель частоты с коффициентом деления Md = 143 на двоично-десятичных счетчиках. Из соотношений (7.72) следует, что для этого требуется не более двух десятичных разрядов, так как (15-102-6)/9 = 166 > 143, а загружаемое число dM = Md - 1 = 142. Поскольку dM = rfjwilO1 + djv/olO0, то можно взять dMi = 14, dMo = 2 или dMi = 13, djv/o = 12. Поэтому можно использовать одно из двух двоичных представлений загружаемого числа dM = DlDlD\Dl.D%D%DfD% = 1110.0010 или 1101.1100. Принципиальная схема 12-разрядного двоичного счетчика с последовательным переносом показана на рис. 7.97,а. В этой же схеме можно использовать и двоично-десятичные реверсивные счетчики 531ИЕ16. Структурная схема многокаскадного счетчика с параллельным переносом и сигналом загрузки L = P4Pie изображена на рис. 7.96,6. Легко убедиться, что программирование модуля пересчета этого счетчика ничем не отличается от программирования модуля пересчета счетчика с последовательным переносом. В частности, модуль пересчета определяется соотношениями (7.69) для двоичного и (7.70) для двоично-десятичного реверсивных счетчиков. Принципиальная схема 12-разрядного двоичного счетчика с параллельным переносом показана на рис. 7.97,6. В этой же схеме можно использовать и двоично-десятичные реверсивные счетчики 531ИЕ16. Вторая структурная схема многокаскадного счетчика с параллельным переносом и сигналом загрузки L = Pi6 показана на рис. 7.96,в. Как и в соответствующем суммирующем двоичном (двоично-десятичном) счетчике (см. рис. 7.58,е), загрузка числа dM производится на 15 (9) тактов раньше, чем в предыдущих счетчиках. Из этого следует, что модуль пересчета 0 ... 112 113 114 115 116 117 118 119 |