Раздел: Документация

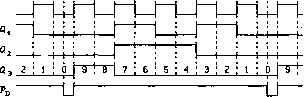

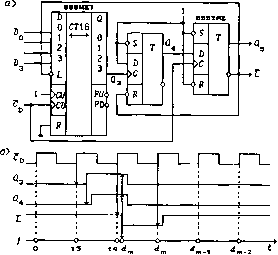

0 ... 115 116 117 118 119 расщепленным тактовым сигналом 555ИЕ6 описывается тактовыми сигналами Су и функциями переноса Ру и заема Pq, которые получаются из соотношений (7.55): С0 = Си V CD, С. = TiC = CuQ3Qo V CDQ0y, C2 = T2C* = Ci/QiQo V CoQiQoV, C3 = T3C = Cy(Q2QxQo V QgQoJv CDQ2Q1Q0, Pu = CuQzQo, Pd = CDQzQ2QxQo, где у = V Qi V Qi (назначение входов i?r, L w. R такое же, что и у счетчика 555ИЕ7). На рис. 7.116,а показаны временные диаграммы, поясняющие работу счетчика 555ИЕ6 в режиме суммирования, а на рис. 7.116,6"- в режиме вычитания. Каскадирование счетчиков с расщепленным тактовым сигналом. Наиболее просто каскадирование счетчиков с расщепленным тактовым сигналом осуществляется соединением выходов переноса Ру и заема Ро предыдущей ИС со входами Су и Со последующей ИС (рис. 7.117). При этом получается асинхронный импульсный счетчик. Его быстродействие не зависит от числа ИС. Реверсивные двоичные счетчики производят счет в дополнительном коде, если старший разряд считать знаковым. Так, при вычитании счетчик, состоящий из тп триггеров, из нулевого состояния переходит в состояние j = 2Ш - 1, т. е. все триггеры изменяют состояние с 0 на 1, и полученный код соответствует числу -1 в дополнительном коде. На рис. 7.118 показана схема счета в прямом коде, выполненная на двух счетчиках 555ИЕ7. Управление счетчиком производится двумя сигналами - х2 и х\. Сигнал х2 задает направление счета: х2 = 0 - сложение, х2 - 1 - вычитание. Сигнал х\ представляет собой импульсы, подлежащие счету со знаком, определяемым сигналом х2. Число N поступивших на счетчик импульсов представляется в прямом коде [N\\\ = Qs-Qi -Qo, где Qs - знак числа (Qs = 0 - число положительное, Qs = 1 - число отрицательное), q7q6q5q4q3q2q1q0 - модуль числа. При счете в прямом коде при х2 = Qs должно производиться сложение, а при х2 ф Qs - вычитание. Поэтому направление счета должно определяться значением сигнала fs = x2®Qs при использовании показанного на рис. 7.118 демультиплексора 1 -► 2, выполненного на ЛЭ И-НЕ. Изменение значения знакового разряда Qs должно происходить после достижения нулевого состояния счетчика при х2 ф Qs в следующем такте. Это обеспечивается подачей сигнала заема на тактовый вход триг- a -+Ч-Н-I-b q, j 8 j 9 I 0 j 1 I 2 3; 4 6 : 7 гт +-t- -4-t- 1 Г t it  Рис. 7.116

P"u«

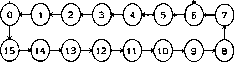

d 0.4 0 - 1 2 3 Ф L XXI сп 6 PU. 0 1 2 3 - a Рис. 7.117 cm- iGh: 1 bbbthz 4 a a d H 0 1 2 4 3 ЛЛ1 >CD ct16 H 0 1 - 2 H 3 l ?d4- >CD сп 6 PD6-. гера знака. При изменении значений Qs ка выходах демультиплексора появляются кратковременные ложные значения сигналов. Для их блокирования на входы R счетчиков подан сигнал Рд, удерживающий счетчик в нулевом состоянии на время переходных процессов в демультиплексоре. со tf СПб .Н-1-1-н н-Ь н-1-  = 6, *D = 6  Рис. 7.119 Программирование модуля пересчета счетчиков с расщепленным тактовым сигналом. На рис. 7.119,а показано включение счетчика 555ИЕ7 на вычитание с записью сигналом L - Ро = 0 числа d\f = 6. Временные диаграммы, поясняющие работу счетчика при таком включении, показаны на рис. 7.119,6. Длительность сигнала загрузки L = 0 определяется быстродействием счетчика и составляет 30 ... 40 нс, что может оказать влияние на надежность срабатывания счетчика. Так как загрузка асинхронная потенциальная, то переход, обозначенный на графе переходов пунктиром (рис. 7.119,в), выполняется в том же такте, что и переход из внутреннего состояния j - eQ3eQ2eQ1eQ0 = 0001 в состояние j = eQ3eQ2eQ1eQ0 = 0000, т. е. за один такт осуществляются два перехода. Это приводит к уменьшению модуля пересчета на 1 по сравнению с синхронной загрузкой числа d\f, а также к уменьшению быстродействия счетчика (максимально допустимой частоты тактового сигнала). Из графа переходов следует, что модуль пересчета Мо = 6 при работе счетчика на вычитание и загрузке числа d\t = 6. В общем случае модуль пересчета двоичных реверсивных счетчиков с асинхронной потенциальной загрузкой Мо = dM,2<dM< 15; Мц = 15 - dM, 0 < dM < 13, (7.86) где d\f = D3D2DiD0, Мо - модуль пересчета при работе счетчика на вычитание, Мц - модуль пересчета при работе счетчика на сложение. со

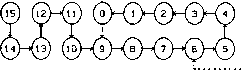

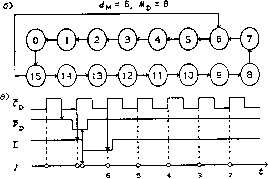

щ PZX>  о 13 6 Рис. 7.120 В схеме, изображенной на рис. 7.119,а, можно использовать и двоично-десятичный реверсивный счетчик 555ИЕ6, при включении которого на вычитание допускается загружать числа dM = 2,3,..., 15 (рис. 7.119,г). Модуль пересчета двоично-десятичных реверсивных счетчиков с асинхронной параллельной загрузкой определяется соотношениями: * Мо = dM, 2 < dM < 15; My = 9 - dM, 0 < dM < 7, (7.87) где d\f = D3D2D1D0. На рис. 7.120,а показано включение счетчика 555ИЕ7 на вычитание с квазисинхронной загрузкой чи- ела d\f = 6. D-триггер задерживает сигнал заема Рц на один такт, поэтому загрузка числа d\f = 6 производится в состоянии счетчика j = 15, а не в состоянии j = 0 (рис. 7.120,6), и на загрузку числа d\f затрачивается один такт (квазисинхронная загрузка). Из графа переходов (рис. 7.120,6) следует, что Мо = 8. Временные диаграммы, поясняющие работы вычитающего счетчика при загрузке числа d\f = 6, изображены на рис. 7.120,в. В общем случае модуль пересчета для схемы, изображенной на рис. 7.120,а, определяется соотношениями: MD = dM+2, 1 < dM < 15; Mv = 17-dM, 0 < dM < 14, (7.88) где dM = D3D2D1D0, 3 < Md, M\j < 17. Длительность значений выходных сигналов счетчика PD = lnL = PD = Q равна периоду тактового сигнала Сd- На рис. 7.121,а приведена схема счетчика с программируемым модулем пересчета, выполненная на основе универсальной схемы временной привязки (УСВП; см. рис. 5.132). Временные диаграммы, изображенные на рис. 7.121,6, поясняют работу вычитающего счетчика при загрузке числа d\i - УСВП обеспечивает проведение квазисинхронной загрузки в состоянии счетчика j = 14. Модуль пересчета Md = Л/ + 3. Общая формула, определяющая модули пересчета двоичного реверсивного счетчика с УСВП, имеет вид: М - 8 при 0 < dj < 7, М + 8 при 8 < dM < 15, (7.89) где dM = D3D2DiD0, М = 24 - dM + 2. Программируемый 12-разрядный двоичный асинхронный реверсивный счетчик с асинхронной потенциальной загрузкой данных представлен на рис. 7.122. Надежность его работы ниже надежности работы 4-разрядного счетчика из-за возможного различия в быстродействии ИС, что более вероятно, чем значительное различие быстродействия триггеров внутри ИС. Модули пересчета этого счетчика определяются выражениями: MD = dM,2<dM< 2™ - 1, Mv = 2m - 1 - dM = Im, 0 < dM < 2т - 2, где т = 12, dM - Dh £h-Do-Программируемый 12-разрядный двоичный асинхронный реверсивный счетчик с квазисинхронной загрузкой данных приведен на рис. 7.123. Надежность его работы гарантирована, так как длительность активного уровня сигнала загрузки L равна MD = dM + 3, 0 < dM < 15, Мц = (7.90)  Рис. 7.121 с 1 2 3 1 ->си ->Сд СТ16 1 ->си ->Сд СПб 1 - 2 <2т » Ч о 1 2 3 >CU >СЪ СПб Рис. 7.122 d 0 Ч 1 2 С - С >d 3 4 г. СПБ d 0 "Ч 1 2 D7 С 1ч>у >d 3 Ф1. СПб 1- 2- с 1Ч>у СПб O11 г55 1-T-9S 0 ... 115 116 117 118 119 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||