Раздел: Документация

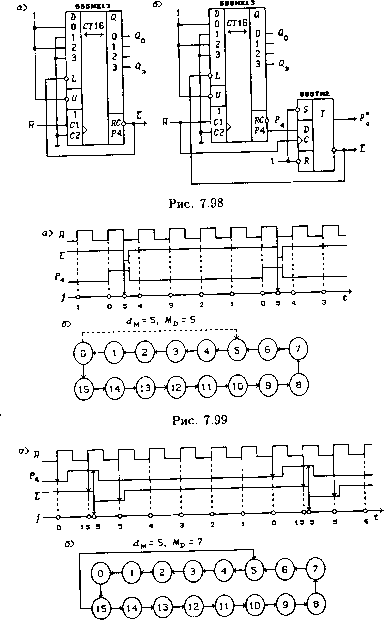

0 ... 113 114 115 116 117 118 119 гт- гт-и- D3-o D7-« ft D у РО E СГ16 oh 1 2 3 Q3 ft СГ16 D -"L U ->C PO E ft СГ16 P46-1-► с CT- ft D I и ьс РО E СП 6 ft D U >C PO E СП 6 CT16 >4Л 1- 1 Dn-e 4 D >L >c PO E CT16 ft 4 D L у t>c PO E ft CT16 3 1» ->c CT16 1 2 Рис. 7.97 двоичного реверсивного счетчика с параллельным переносом и сигналом загрузки X = Pi6 определяется выражениями: MD = dM- 14, 24<dM<2m~ 1, Ma = 2m - 15 - dM, 0 < dM < 2m - 24 - 1 (m = 16 - число двоичных разрядов счетчика), а двоично-десятичного реверсивного счетчика - выражениями: MD = dM+l, 10<dM< 15-(10m-l)/9, 1 Mv = 10m - 9 - dM, 0 < dM < Ют - Ю1 - 1, J где m = 4 - число десятичных разрядов счетчика, Md - модуль пересчета вычитающего счетчика при допустимых значениях разрядов 0 < dMi = D3D2D\D0 < 15 и чисел 10 < dM < 15 • (104 - 1)/9 = 16665 (t - номер разряда), Му - модуль пересчета суммирующего счетчика при допустимых значениях разрядов 0 < dMi = D3D2D\D0 < 9 и чисел 0 < dM < Ют - 11, з dM = £ rfA#.-10* = Dl... Dl.Dl ...Dl.D\...Dl.D°3... D°0. Принципиальная схема 12-разрядного двоичного счетчика с параллельным переносом и сигналом загрузки l = р\§ показана на рис. 7.97,в. В этой же схеме можно использовать и двоично-десятичные реверсивные счетчики 531ИЕ16. Наибольшее быстродействие имеют программируемые счетчики, представленные на рис. 7.96,5 и 7.97,6, так как активный уровень сигнала l = 0 определяется значением переноса р4 = 0, который без задержки подается по параллельной цепи на ЛЭ ИЛИ. При использовании ИС 531ИЕ17 экспериментальные максимальные значения /тах частоты тактового сигнала н при программировании любого модуля пересчета 16-разрядных двоичных счетчиков составляют 17 МГц для счетчика, выполненного по рис.7.96,а, 27 МГц для счетчика, выполненного по рис.7.96,6, и 21 МГц для счетчика, выполненного по рис.7.96,е. Программирование модуля пересчета счетчиков с асинхронной загрузкой данных. Загрузка чисел dj при программировании модуля пересчета асинхронным потенциальным сигналом l = 0 производится немедленно без воздействия импульсного сигнала dH = 1, по которому при счете совершаются переходы внутренних состояний счетчика. На рис. 7.98,а показано включение счетчика 555ИЕ13 на вычитаниес записью сигналом l = rc - р4н - 0 числа d\j = 5, где р4 = Q3Q2Q\Qq-Так как при этом внутреннее состояние счетчика j = 0 изменяется на состояние j = 5 (рис. 7.99,а; j = eQ3eQ2eQ1eQ0, где egr = 0 или 1), то длительность сигнала l = 9 определяется лишь быстродействием ИС, т. е. сигнал l - dP4H = P4dH - импульсный сигнал с низким (0) активным уровнем. На рис. 7.99,6изображен граф переходов, описывающий работу счетчика 555ИЕ13 при программировании модуля пересчета, - переход, обозначенный штриховой линией, выполняется в том же такте, что и переход из состояния j = 1 в состояние j = 0, т.е. за один такт осуществляется два перехода. Из графа переходов следует, что модуль пересчета счетчика Мр = 5 - на 1 меньше, чем в счетчике с синхронной загрузкой данных, изображенной на рис. 7.94,а. Аналогично можно показать, что при подаче на счетчик, представленный на рис. 7.98,а, сиг-  нала U = 0 (включение на сложение) модуль пересчета Ми будет равен 10. В общем случае модуль пересчета двоичного реверсивного счетчика с асинхронной загрузкой данных задается выражениями: MD = dM, 2 < dM < 15; Mv = 15 - dM, 0 < dM < 13, (7.75) где dM = D3D2DiD0. Основным недостатком рассмотренного метода программирования модуля пересчета является уменьшение быстродействия счетчика из-за срабатывания триггеров дважды за один такт при загрузке данных d\f (максимально допустимая частота тактового сигнала уменьшается, по меньшей мере, в два раза). Кроме того, в принципе возможны, хотя и маловероятно, сбои в работе счетчика из-за недостаточной длительности импульсного сигнала L для некоторых триггеров счетчика (если бы триггеры сильно различались по быстродействию, то счетчик не смог бы работать правильно). В схеме, изображенной на рис. 7.98,а, можно использовать и двоично-десятичный реверсивный счетчик 74X5190 (см. рис. 7.83), модули пересчета которого будут определяться соотношениями: MD = dM, 2 < dM < 15; Ми = 9 - dM, 0<dM<7, (7.76) где dM = D3D2D1D0. На рис. 7.98,6"показано включение счетчика 555ИЕ13 на вычитание с квазисинхронной загрузкой числа df = 5, или конвейерным переносом. Сигнал переполнения Р4 задерживается .D-триггером на один такт (рис. 7.100,а), поэтому загрузка числа djvf производится в состоянии счетчика j = 15, а не в состоянии j = 0 (рис. 7.100,6), и на загрузку числа d\f затрачивается один такт (квазисинхронная загрузка). Из этого следует, что модуль пересчета определяется соотношениями: MD - dM + 2, l<dM < 15; Mv = 17-dM, 0 <*dM < 14, (7.77) где dM = D3D2D!D0, 3 < MD, Mv < 17. Из этих выражений видно, что модуль пересчета может быть больше 24 = 16. В принципе, цифровой автомат, содержащий пять триггеров, может иметь 25 = 32 внутренних состояния. Хотя 4-разрядный счетчик не может иметь более 16 внутренних состояний, однако некоторые его состояния под управлением /-триггера могут повторяться дважды за цикл пересчета. Так, при значении управляющего сигнала U - 1 (вычитание) и загрузке числа df = 15 внутреннее состояние счетчика j = 15 устанавливается в двух последовательных тактах. Длительность активного уровня задержанного сигнала переполнения счетчика Р4 = L равна периоду тактового сигнала Я, поэтому надежность срабатывания всех триггеров счетчика гарантирована. Быстродействие счетчика с квазисинхронной загрузкой не ниже быстродействия счетчика с синхронной загрузкой, если задержка сигналапереполнения Р4 в счетчике относительно тактового сигнала II не меньше задержки сигнала L в jD-триггере. Если в схеме на рис. 7.98,6 двоичный счетчик заменить на двоично-десятичный реверсивный счетчик 74X5190, то модули пересчета будут определяться выражениями: MD = dM + 2, 1 < dM < 15; Aft/ = 11 - dM, 0 < dM < 8, (7.78) где dM = D3D2DiD0. Задержка сигналов переполнения P4 и RC в ИС 555ИЕ13 относительно тактового сигнала Н несколько больше задержки выходных сигналов триггеров Qr, поэтому повысить быстродействие программируемого счетчика можно использованием сигналов Qr для загрузки данных о?д/. На рис. 7.101 приведена схема счетчика с программируемым модулем пересчета, выполненная на основе универсальной схемы временной привязки (УСВП; см. рис. 5.132).

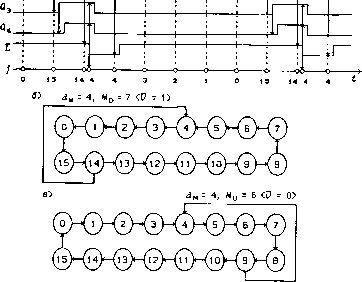

I- D ->С Се усвп D -ЬС Рис. 7.101 Временные диаграммы, изображенные на рис. 7.102,а, поясняют работу вычитающего счетчика для случая загрузки числа d\f = 4 - УСВП обеспечивает проведение квазисинхронной загрузки в состоянии счетчика j = 14. Из графа переходов (рис. 7.102,6) следует, что модуль пересчета Md = 7 = + 3. В суммирующем счетчике его старший разряд Q3 изменяется с 0 на 1 при переходе из состояния j> = 7 в состояние j = 8. Значение сиг-  Рис. 7.102 нала загрузки L = 0 УСВП выдает на такт позже в состоянии j = 9, поэтому модуль пересчета Мц = 6 при квазисинхронной загрузке числа dM = 4 (рис. 7.102,е). В общем случае модули пересчета двоичного реверсивного счетчика с квазисинхронной загрузкой данных с помощью УСВП задаются выражениями: М - 8 при 0 < dM < 7, М + 8 при § < dM < 15, (7.79) где dM = D3D2DXDG, М = 24 - dM + 2. Из этих выражений видно, что модуль пересчета может быть равен 18. Под управлением УСВП некоторые состояния счетчика могут повторяться дважды за цикл пересчета. Так, при значении управляющего сигнала U = 1 (вычитание) и загрузке числа dm = 15 последовательность внутренних состояний счетчика j = 15 и 14 повторяется два раза за цикл пересчета. Программируемый 12-разрядный двоичный реверсивный счетчик с последовательным переносом и асинхронной потенциальной загрузкой данных представлен на рис. 7.103. Надеж- dM + 3,0<dM< 15, Ми = I 0 ... 113 114 115 116 117 118 119 |