Раздел: Документация

0 ... 54 55 56 57 58 59 60 ... 78 I I I 5Г I Рис. 19.1. Зависимость числа операций, выполняемых на дном кристалле, от тактовой частоты В качестве типичного примера рассматриваема разработка цифрового фильтра с улучшенными параметрами. От этого фильтра требуется обработка входных данных, поступающих со скоростью I (t I 4-107 оп./с с разрешающей способ- } 7ЮЮО«--- --------- - - ииностью по частоте 10 кГц. Фильтр Тактовая частота, МГц1 1реализуется с помощью вычисления спектра по 4096 входным отсчетам, умножения этого спектра на заданную частотную характеристику и, наконец, обратного преобразования для получения выходного сигнала во временной области. Указанная последовательность операций выполняется для новых данных, перекрывающихся на 50% длительности преобразования со старыми, с целью исключения граничных эффектов. Такая система потребует объема вычислении, эквивалентного примерно 1 млрд двоичных "бабочек" БПФ в секунду (240 млн. бабочек для двух операций прямого и столько же для двух операций обратного преобразования) . Технически задача решается преобразованием входного потока данных со скоростью 4 • 107 оп./с в четыре потока со скоростью 10* оп./с. Эти четыре потока обрабатываются с помощью конвейерного процессора БПФ, реализующего алгоритм Кули-Тьюки с основанием четыре, в юответствии с разработкой [1]. Алгоритм Кули-Тьюки был выбран потому, что как прямое, так и обратное преобразования вычисляются по схемам, (остоящим из двух основных вычислительных элементов. Согласно алгоритму, предложенному в [1], примерно 10 лет назад было разработано семействе» ЭСЛ малой степени интеграции фирмы General Electric. Это семейство содержит 27 000 интегральных схем для выполнения 960 млн двоичных бабочек БПФ в секунду [1]. Рассматриваемое здесь устройство по своим характеристикам сопоставимо со своим предшественником, но для реализации потребовалось в пять раз меньше ИС. В этом устройстве для представления каждой составляющей комплексных данных использовались 22-разрядные числи с плавающей запятой вместо 11 -разрядных чисел с фиксированной запятой с 6 разрядами для порядка в варианте фирмы General Electric. 19.2. ТРЕБОВАНИЯ К ФИЛЬТРУ Структура алгоритма обработки показана на рис. 19.2. Шток входных данных (в верхней части рис. 19.2) через блок сбора данных поступает в блок вычисления 4096-точечного комплексного БПФ (4К БПФ). Обработка с использованием функций окна по временной области осуществляется в блоке сбора данных. Преобразованные таким способом входные данные затем фильт-346 Входные данные о-   Блок Вычисления сам I I I \ \ \

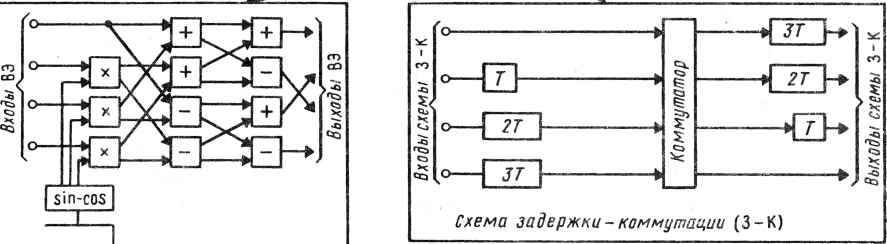

блок Вычисления сам основные операции фильтра Фильтр в яоетотнои области  Выходные сигналы (довременной области)  Фильтр В частотной области tfK обратное БПФ П I I \ \ I I jepejbjdmj<amji обработки Рис. 19.2. Структурная схема фильтра для обработки сигналов в частотной области руются путем умножения в частотной области с последующим вычислением обратного БПФ. После БПФ вычисляется модуль нефильтрованного спектра для получения спектральной плотности мощности (СПМ), который затем используется для выполнения основной операции фильтра. Аналогичный процесс выполняется и для данных, сдвинутых по времени (на половину длительности периода преобразования) в канале с перекрытием. Использование двух таких каналов с перекрытием предотвращает потери на границах за счет использования функций окна. Как видно из приведенной структуры алгоритма, необходимыми являются следующие блоки: 1)блок сбора данных - обеспечивает входной интерфейс, преобразование одного канала со скоростью 4 • 107 оп./с в четыре канала со скоростью 107 оп./с и взвешивание во временной области любой предварительно запомненной функцией окна (для сравнения функций окна можно обратиться к [2]); 2)блок 4096-точечного комплексного БПФ - принимает данные в последовательном во времени порядке и выполняет операции комплексного БПФ. Блок является программируемым для выполнения преобразований длительностей, кратных степени 4 (т.е. 4,16, 64, 256, 1024, 4096); 3)блок фильтрации в частотной области - умножает спектр, полученный в результате БПФ, на частотную характеристику фильтра. Эта операция представляет собой простое поточечное перемножение; 4)блок вычисления спектральной плотности мощности - вычисляет спектральные составляющие, упорядочивает данные в порядке следования частот и выполняет операцию усреднения с экспоненциальным взвешиванием; 5)блок основной операции фильтра - представляет собой универсальную ЭВМ, реализующую адаптивный фильтр, основанный на использовании наблюдаемой спектральной плотности мощности; 6)блок 4096-точечного комплексного обратного БПФ - вновь преобразует обработанный в фильтре спектр мощности во временную область. Схема обратного БПФ является программируемой (аналогично схеме прямого БПФ) для выполнения преобразований входных данных разной длительности. Таким образом, требуется шесть основных блоков. Следует подчеркнуть, что уровень сложности указанных устройств различен; наиболее сложными из них являются блоки для выполнения прямого и обратного БПФ. После первоначальной обработки в блоке сбора данных все последующие вычисления выполняются с помощью арифметических операций над 22-разрядными числами с плавающей запятой (6 разрядов - порядок, 16 разрядов - мантисса) для сохранения точности и исключения необходимости в адаптивном масштабировании данных. В рассматриваемом процессоре используется конвейерная обработка данных четырех параллельных каналов с каскадной архитектурой [3]. Этот способ построения был выбран для обеспечения высокого быстродействия (для обработки 4 • 107 оп./с) с использованием в то же время су шествующей технологии СБИС (как отмечалось во введении, тактовая частота современных ИС составляет обычно порядка 10 МГц; для более высоких скоростей обработки потребуются специальные ИС с существенно меньшим уровнем интегращи). В настоящее время имеется большое разнообразие компонентов СБИС, реализуемых на базе различных технологий, обеспечивающих значение тактовой частоты 10 МГц. Примерами таких устройств являются быстродействующая ЗУПВ емкостью 16 Кбит, 22-разрядные сумматоры и умножители с плавающей запятой и другие устройства [4]. 19.3. РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНЫХ БЛОКОВ Здесь будет дан обзор конструкций основных блоков устройства обработки, арифметические функциональные элементы которого выполнены на одном кристалле. Блок сбора данных. Этот блок обеспечивает интерфейс с источником данных, распределяет поток входных данных по четырем каналам и выполняет взвешивание во временной области с использованием функций окна. Схема реализации блока показана на рис. 19.3. Данные в комплексной форме, поступающие с тактовой частотой 40 МГц, загружаются в восемь сдвиговых регистров по четыре для каждой из двух комплексных составляющих данных. Содержимое каждого из регистров затем передается в восемь параллельных фиксаторов с тактовой частотой 10 МГц. С помощью сдвигового регистра и фиксатора осуществляется переход от одного последовательного комплексного канала к четырем параллельным каналам комплексных данных. Данные четырех параллельных каналов подвергаются весовой обработке с использованием функции окна (шириной в 1024 отсчета [2]), хранящейся в постоянном запоминающем устройстве (ПЗУ). Это ПЗУ содержит четыре параллельных канала памяти, каждый из которых содержит 1024 весовых коэффициента, так как все четыре канала работают одновременно. В этом блоке сдвиговые регистры и фиксаторы выполнены на элементах ЭСЛ для достижения тактовой частоты 4 • 107 оп./с. Поскольку для элементов ЭСЛ характерна довольно низкая плотность на единицу площади, то в 348 Входные /I °-данные iqc Сдвиговый регистр сдвиговый регистр сдвиговый регистр Сдвиговый регистр j сдвиговый регистр Сдвиговый регистр Сдвиговый регистр сдвиговый регистр Генератор тактовых импульсов WMfu, т4 16 Фиксатор)" ХФиксатср\ АФиксатор (" 1 Х •\ Фиксатор АФикситор А Фиксаторе : Т I 11 .У" 10МГц Счетчик адреса 16 10 tcz> ПЗУ с коэффициентами фу мк ции окна. ту еп ] Поток (q) г данных 1 Ш 1 Поток Ш) I данных 2 (I) Поток (q) ( данных 3 (I) 1 Поток ((Г) ( данных 4 4 Рис. 19.3. Структурная схема блока сбора данных одном кристалле можно разместить только четыре регистра или фиксатора. Умножитель и ПЗУ выполнены в виде СБИС, поэтому для построения всего блока потребуется около 120 БИС, но только 15 из них БИС ЭСЛ. Предполагается, что входными данными являются 16-разрядные слова с фиксированной запятой. Поскольку точность большинства быстродействующих АЦП низка (8,10, реже 12 разрядов), то в данном блоке можно использовать входные слова меньшей длины. Из-за низкой степени интеграции схем ЭСЛ уменьшение длины входных слов до 12 или 8 разрядов снижает сложность от 25 до 50% соответственно. С учетом приведенных данных была выбрана с запасом 16-разрядная длина слова. Блок БПФ. Как уже отмечалось, блок БПФ оказывается сложнее других блоков. В результате для целей реализации блок разделен на функциональные элементы двух типов. Такое разделение позволяет использовать преимущества конвейерного алгоритма БПФ Кули-Тьюки. Структура процессора БПФ показана на рис. 19.4. Процессор построен на базе вычислительных элементов (ВЭ) и элементов задержки - коммутации (3 - К). В этом проекте вычислительный элемент реализует бабочку БПФ с основанием 4, а элемент задержки - коммутации осуществляет преобразование данных, необходимое для обработки с использованием алгоритма Кули-Тьюки [5]. Основной принцип конвейерной обработки был разработан в конце 1960-х годов [6], а затем он был распространен на БПФ с основанием 4 [1]. Алгоритм БПФ с основанием 2 в настоящее время реализуется на СБИС с аналогичным разделением схем на два типа [7]. Вычислительный элемент для бабочки БПФ с основанием 4 реализует 4-точечное дискретное преобразование Фурье. Для выполнения этой операции требуется три умножителя комплексных чисел, восемь сумматоров Входные} данные ] ВЗ 3-К 256 ВЗ з-к 6h вэ з-к 7£

} Выходные [преобразованные ) данные  Счетчик Вычислительный элемент Рис. 19.4. Структурная схема блока вычисления БПФ с основанием 4 с помощью конвейерного алгоритма Кули-Тьюки комплексных чисел (четыре выполняют суммирование, а остальные четыре - вычитание), таблицы функций sin, cos (хранящиеся в ПЗУ) и различные логические адресации. Для реализации вычислительного элемента потребуется около 80 ИС. Такой невысокий уровень сложности является прямым результатом наличия однокристальных арифметических устройств. Вторым элементом конвейерного БПФ является элемент задержки - коммутации, используемый для выполнения необходимых преобразований данных для их обработки с помощью алгоритма Кули-Тьюки. Элемент состоит из входных линий задержки калиброванной длительности, коммутатора и выходных линий задержки тоже калиброванной длительности. Длительность задержки в элементе задержки равняется единице на последнем этапе БПФ и увеличивается с коэффициентом 4 на каждом предшествующем этапе. Для осуществления преобразования длиной 4096 разрядов потребуется около 180 ИС. Способ получения задержек показан на рис. 19.5. Запоминающее устройство с произвольной выборкой используется для последовательной записи данных (по сумме значения счетчика и сдвига в качестве адреса) и считывания (по значению счетчика в качестве адреса). Таким образом, данные записываются в память последовательно (как это было бы в запоминающем устройстве на магнитном барабане с последовательной выборкой) и считывание задержанных данных также осуществляется последовательно. В своей основной форме конвейерного БПФ с основанием 4 вычисляются преобразования последовательностей данных, длины которых являются степенями числа 4. Добавление вычислительного элемента с основанием 2 (являющегося частью вычислительного элемента с основанием 4) и специального элемента задержки - коммутации позволит осуществлять вычисление преобразований, длина которых является степенью числа 2. рис. 19.5. Схема реализации временной задержки Входные данные i Счетчик ЗУ с произвольной Выборкой адреса данных Мультиплексор 2:1 7 Задержка Задержанные данные Блок фильтрации в частотной области. Операция фильтрации в частотной области включает поточечное умножение 4096-точечного комплексного спектра на частотную характеристику фильтра. Блок реализован с использованием четырех идентичных комплексных каналов, как показано на рис. 19.6. Частотная характеристика фильтра записана в запоминающем устройстве с произвольной выборкой и вызывается из памяти по мере поступления входных данных. Этот блок реализуется с использованием примерно 70 ИС. Блок вычисления спектральной плотности мощности (СПМ). Этот блок используется для вычисления оценки спектральной плотности мощности (суммированием квадратов действительной и мнимой составляющих на каждой частоте спектра) и усреднения последовательных СПМ с помощью рекур- Рис. 19.6. Структурная схема блока фильтра в частотной области to V: си Р а; Тэ Тэ со ч Коэффициенты фильтра Управление нагрузкой о-фильтра Адрес коэффициента о-фильтра «и та ЗУ С произвольной выборкой I Мультиплексор 7 Счетчик адреса 0 ... 54 55 56 57 58 59 60 ... 78 |