Раздел: Документация

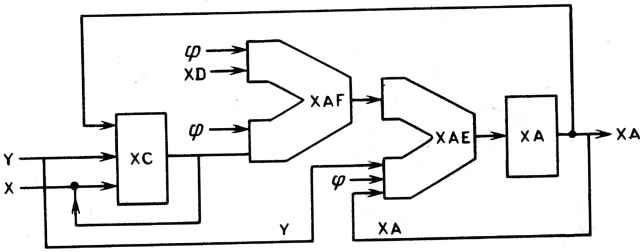

0 ... 52 53 54 55 56 57 58 ... 78 при сложении с плавающей запятой иногда требуется иметь такую последовательность микрокоманд SNMPL + UV-->UV MP + UV:CS-> UV в которой два этих результата умножения представляют сдвинутые вправо младшую и старшую части мантиссы второго слагаемого соответственно. Если принять, что мантисса первого слагаемого находится в паре регистров UV, то условие переполнения может встретиться в любой из двух операций сложения. Однако поскольку операция является простым сложением двух чисел, одно из которых уже сдвинуто вправо, может произойти не более одного переполнения. Так, если регистр W содержит масштаб (порядок) большего из двух операндов (считаем, что это первое слагаемое), то следующая операция в сумматоре II скорректирует масштаб при возможном возникновении переполнения и выполнит сдвиг вправо: W + LGCO - W (откуда следует, что HCI = LGCO) . Вторым случаем, при котором может встретиться переполнение, является операция нормализации на 1 разряд. Код для него задается выражением UV + UV:CS-> UV Содержимое пары UV будет сложено с самим собой, давая сдвиг на 1 разряд влево; если это вызывает переполнение, то операция условного сдвига сдвинет его обратно, оставляя результат нормализованным в любом случае. Следовательно, если произошло переполнение, масштаб должен остаться прежним; если же переполнения не было, масштаб должен быть уменьшен на единицу. Это может быть выполнено следующей операцией сумматора Н: W - 0 - 1 + LGCO > W которая может быть осуществлена подачей содержимого W на вход А этого сумматора, 0 на вход В, выхода переноса СО - на вход переноса сумматора Н и установкой СО в регистре LGCO. Еще одним случаем возникновения переполнения является умножение двух чисел, которые представляют отрицательные степени числа 2. Такие числа будут иметь мантиссы 10000000 (8-разрядное двоичное представление), которые представляют -1. Произведение двух таких чисел в дополнительном коде должно быть положительной степенью числа 2, а будет - отрицательной (произведение 22LS). Однако дополнительный 17-й разряд умножителя будет истинным знаковым разрядом, вычисленным с помощью операции "Исключающее ИЛИ" входных знаковых разрядов. Таким образом, результатом будет (в 8-разрядном формате, принятом в примерах) 01000000 00000000 и операция MP + 0:CS-+UV скорректирует переполнение сдвигом вправо и запомнит в регистре UV число 010000000 00000000 Затем в следующем цикле операцией W + LGCO -> W должен быть скорректирован масштаб. 18.5.4. Контроллеры адреса матричной памяти В кристалл АУО встроены контроллеры адресов ячеек памяти X и Y. Используются два одинаковых 16-разрядных контроллера. В каждом контроллере используются два 16-разрядных сумматора и два 16-разрядных регистра. Структурная схема контроллера адреса X(ХА) показана на рис. 18.5. При такой структуре контроллера адреса предполагается наличие номера базового адреса (Y) с индексом (ХС) и переменной смещения (XD) . Предусмотрена функция инкремента-декремента смещения по столбцам для прямой адресации двумерных массивов. Например, прямая двумерная адресация с маскированием при свертке обеспечивается так, как показано на рис. 18.6. Размер маски ограничивается величиной, равной удвоенному максимальному значению XD плюс единица (девять для данного АУО) . Выбор данных из ячеек X и Y в качестве источника для индекса ХС позволяет использовать память X  Рис. 18.5. Контроллер адреса X база-У Двумерный процесс свертки с маскированием хс Mill1 г-ГТ" rTtrhrH-4 + tt-t-+-м~ ~~\ I -f"~t"T~Т~f"t" -4-4--+-h-1-4--+--+-+- j i i i i i I i i Команды адресации XD 1.XA= XA-XC-2 2.= X A +1 3.=XA +1 4.= ХД+XC-2 5.= X A +1 6.=XA +1 7.=XA+XC-2 8.=XA +1 9.=XA +1 1 XA = XA-XC-2 Рис. 18.6. Двумерная адресация с маскированием 335 как буфер для массивов, размерность которых больше двух. Разумеется, адресный контроллер Y может быть использован разработчиком микропрограмм как дополнительный контроллер адреса, работающий параллельно. 18.6. ВЫБОР ФУНКЦИЙ КРИСТАЛЛА Очевидно, что кристалл АУО будет выполнять базовые функции умножения, сложения, накопления. Однако размещение в кристалле локальной памяти умножителя (XL, YL) , реализация в нем специальных логических функций и контроллеров адреса были предметом выбора для разработчика. Важной задачей явилась реализация регистров XL, YL, так как использование шин не должно ограничивать производительность. Нам хотелось использовать умножитель в микропрограммах обработки со 100%-ной эффективностью. Вопросом оставалось лишь число регистров, которое должно быть реализовано. Было найдено, что для рассмотренных задач двух регистров на каждый вход будет достаточно. Аналогично высокий приоритет имели специальные логические функции, так как они прямо влияли на производительность мик ропрограмм. Адресные контроллеры для памяти X и Y были, конечно, не обязательны для арифметического процессора. Их реализация рассматривалась совместно с реализацией либо встроенной памяти программ (ОЗУ или масочное ПЗУ), либо памяти X, Y, либо системного контроллера. В этом главным образом состоял выбор между встроенными и внешними функциями. Кристалл не содержит ОЗУ или ПЗУ - устройств, популярных в новейших процессорных кристаллах. Реализация в кристалле памяти X, Y, R и программной памяти рассматривалась как альтернатива, однако основным аргументам отказа от включения запоминающих устройств в состав кристалла было следующее: 1)полупроводниковая промышленность будет продолжать выпуск все более быстродействующих, с более высокой степенью интеграции КМОП ИС памяти (ППЗУ, ПЗУ и ЗУПВ) ; 2)нужно разработать кристалл, обладающий достоинствами, упомянутыми в п. 1, и не допустить его устаревания по сравнению с выпускаемыми; 3)нужно выпустить такое АУО, чтобы разработчик-прикладник мог использовать память такого типа и такого объема, какие требуются для решения прикладной задачи. Таким образом, мы предвидим создание системы, в которой может использоваться программная память на ППЗУ, ПЗУ или ОЗУ. Очевидно, что программная память на ОЗУ должна загружаться из центральной ЭВМ. Так как команда АУО занимает 80 разрядов, для таких систем предусматривается длина команды от 96 до 128 разрядов. Элементы памяти X, Y, встроенные в кристалл, были бы желательным средством. Но если часть памяти X, Y является встроенной, а другая находится вне кристалла, то разработчик прикладной системы будет ограничен в выборе типа ОЗУ. Для различных применений мы предвидим использование ОЗУ с организацией N X 1 или АХ 8 (в будущем, возможно, NX 16) . 336 Если бы в кристалл был включен системный контроллер для микропрограммного управления, прямого доступа к памяти и управления вводом-выводом, то число выводов превзошло бы 150 и не хватило бы площади для адресных контроллеров. Поскольку микропрограммные контроллеры прямого доступа к памяти были предложены полупроводниковыми фирмами, а контроллеров данных не было, мы решили реализовать функцию управления данными X, Y. 18.7. РАЗРАБОТКА СБИС При реализации в кремнии а риф метического устройства обработки для матричных процессоров проектировщик имеет возможность принимать неоднозначные решения. Важные решения и компромиссы, относящиеся к задаче проектирования СБИС, будут обсуждены в последующих подразделах, чтобы пояснить, как данная ИС стала такой, какая она есть. Будет дано краткое обсуждение выбора технологии, логического и схемотехнического проектирования, выбора и реализации топологии. 18.7.1. Технологический процесс Технологический процесс изготовления АУО - это микроКМОП-процесс (jj. -CMOS). На время разработки данного проекта этот процесс был наиболее совершенным из доступных для КМОП-приборов с кремниевым затвором. Он обладает некоторыми очень важными характеристиками, которые делают его наиболее подходящим для реализации АУО и обеспечивает создание приборов с поликремниевым затвором на основе силицида платины и разрешение 3 мкм. Получение силицид-платиновых затворов в микроКМОП-процессе дает две важные характеристики, которые весьма желательны при разработке сложных быстродействующих шинно-ориентированных ИС. Во-первых, это позволяет использовать как р-, так и «-примесный поликремний без необходимости обычных для данного процесса металлических перемычек для соединения двух различных структур. Замыкание поликремниево! о диода осуществляется силипид-платиновым слоем, расположенным на протравленном поликремнии. Благодаря этой процедуре сохраняются достоинства процесса с поликремнием р- и «-типа. Как правило, этим обеспечивается контакт (скрытый) между поликремнием и подложкой. Такая гибкость прибора позволяет экономить полезную площадь кристалла из-за обеспечения возможности выполнения всех типовых соединений выводов транзистора с соседними элементами в поликремнии без использования металла. Другим решением проблемы р«-вентиля является использование высокопримесного поликремния одного типа проводимости (обычно «-типа). Это устраняет необходимость в перемычках между элементами, однако обеспечивает скрытые контакты истока или стока только для приборов «-типа и поэтому приводит к менее эффективному размещению, чем то, которое получается с силицидом платины. Еще одним фактором является очень низкое сопротивление поликремния. При разводке и проектировании СБИС это весьма желательное достоинство - 337 низкое сопротивление поликремния - проявляется в двух направлениях. Получаемое при этом удельное сопротивление 2 - 5 Ом по сравнению с 20 - 30 Ом для однопримесного и-поликремния означает семикратное уменьшение задержки (RC) типового соединения. Даже если только небольшая часть общей задержки прибора определяется jRC-задержками, разработчик может обойти те трудности в увеличении дополнительной площади кристалла, которые существуют при использовании технологических процессов без силицида платины. Это приводит ко второму достоинству низкорезистивного поликремния, которое заключается в гибкости, предоставляемой разработчику топологии, поскольку не требуется дополнительная площадь кристалла для обеспечения межсоединений в высокоскоростных цепях прибора. В данном КМОП-процессоре используются приборы с размером затвора 3 мкм, а размеры элементов обеспечивают задержку 2 - 3 не на вентиль. Такое быстродействие достаточно велико для обеспечения работы АУО с частотой более 4 МГц и с мультиплексированным портом микрокоманд и портом R-шины, работающими с частотой 16 МГц. Процесс позволяет получить КМОП-приборы с напряжением 5 В, и сигналы СБИС совместимы с уровнем ТТЛ. Потребляемая мощность кристалла составит менее 200 мВт. 18.7.2. Логическое и схемотехническое проектирование При проектировании данной схемы использовались стандартные приемы проектирования КМОП ИС. Качество проектирования основных схем было проверено реализацией по нескольким технологиям. Например, в разработке широко использовалась схема матричного сумматора, запатентованная фирмой Motorola [5]. Использование проверенных узлов минимизировало риск ошибок разработки, приводящих к дорогостоящему перепроектированию и задержкам графика разработки. Процесс разработки схемы был постоянным компромиссом между временем и стоимостью проектирования и рабочими характеристиками прибора. Как только цели по обеспечению требуемых характеристик прибора достигались, усилия по их улучшению прекращались. Характеристики анализировались с помощью моделирования МОП ИС и использования имитатора переходных процессов в схемах, который постоянно коррелировался с измеренными характеристиками контрольных образцов приборов. Суть подхода - проектирование универсального прибора, отвечающего поставленным целям. Однако всегда желательна повышенная производительность. Всегда найдется система, в которой можно использовать большую производительность. Следует отметить, что при данном подходе к проектированию законченный проект не даст наилучших рабочих характеристик, возможных для данной МОП-технологии, но время и стоимость разработки будут находиться на минимально приемлемом уровне. 18.7.3. Подход к топологии Методика разработки топологии определялась ограничениями, накладываемыми на длительность разработки, сложность схемы и ее быстродействие. 338 \ Для того чтобы разработать кристалл с оптимальными производительностью и плотностью, потребовалась бы разработка полностью заказной СБИС. Однако поскольку программа АУО должна была только продемонстрировать возможности реализации матричного процессора, то для проектирования был отведен минимум средств и времени. В этих обстоятельствах наилучшие результаты могли быть получены при использовании топологии полузаказной ИС сразу в нескольких ее местах с введением максимальной избыточности. Наилучший пример повторяемости - ячейка сумматора с ускоренным переносом, которая была применена почти в каждой секции кристалла. Топология этой ячейки, безусловно, не была оптимальной для каждой из секций, где она использовалась. Однако экономия времени и снижение риска, вытекающие из необходимости переразводки полного сумма гора, были расценены как хорошая компенсация потерь площади кристалла. При разработке топологии секций прибора основная методика состояла в упаковке ячеек с наибольшей плотностью в пределах ограничений, продиктованных общим планом кристалла. В этом процессе после соединения ячеек секции, как правило, получалась топология секции, отличная от предполагавшейся и продиктованной общим планом кристалла. В проектах, где основным фактором оценки является плотность упаковки, а не время и стоимость разработки, проводится несколько итераций проектирования топологии секции для оптимизации топологии всего кристалла. В программе же разработки СБИС матричного процессора такие итерации не проводились даже тогда, когда расположение было неудовлетворительным и в жертву приносилась площадь кристалла. При данном подходе время проектирования составило 17 чел.-мес, а разработка топологии заняла 24 чел.-мес. В табл. 18.2 показано, что в приборе содержится 30 500 транзисторов. Определяя "показатель регулярности", предложенный в работе [6], при отсутствии ПЗУ в кристалле и наличии 1207 Таблица 18.2. Распределение площади кристалла

0 ... 52 53 54 55 56 57 58 ... 78 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||