Раздел: Документация

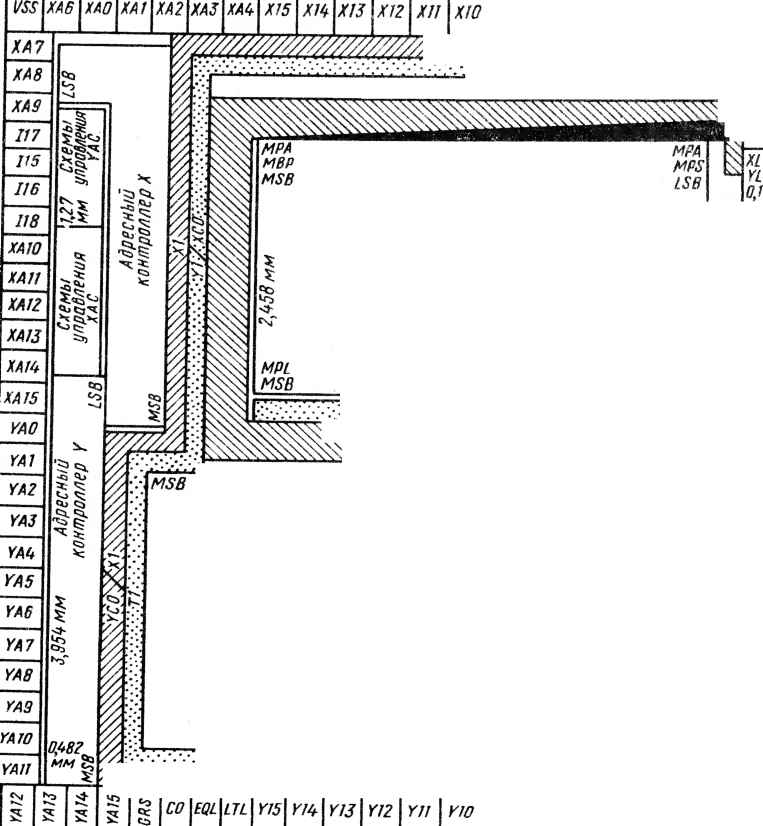

0 ... 53 54 55 56 57 58 59 ... 78 изображений транзисторов получим его значение 25,3. Разумеется, сравни-тельные данные из работы [6] приведены для л МОП-приборов; стоимость нашего проекта была ниже, чем стоимость прибора Gold RISC I. По данным табл. 18.2 могут быть проведены и другие сравнительные оценки с проект-ными характеристиками из работы [6]. На основе общей методологии, продиктованной необходимостью компромиссных решений, разработка топологии СБИС началась с анализа архитектуры. Из архитектуры и таблицы микрокоманд вытекают основные способы соединения на кристалле 20 различных ниш данных, 184 линий управления, питания и земли при обеспечении цикла длительностью 250 не. Было рассмот-рено множество эскизов кристалла и структур соединений, прежде чем была выбрана структура, приведенная на рис. 18.7. 7,569 мм Умножитель 4,7/4 мм MPL MPR LSB MSB  X9 Х8 Х7 Х6 Х5 х с пав) у Регистры xi, гi (2-15)  WUHQR(!6) MPR LSB v., .• .Шина MPt /мря/У-. Регистры команд и дешифраторы для регистров XL, YLyX0UT и умножителя юг R13 118 10 JZ 13 14 Шина XS, YS(32) Сумматоры а регистры со схемами диагностик, плавающей запятой и масштабирования X г Ь£Ь8 мм Vff/б); {Усилители [синхррсиг-шпоВ Y9 Y8 Y7 тт7 Y6 Y5 Регистры команд и дешифраторы для сумматоров и регистров 15 16 17 YDD JCL SYCL 19 110 т 1,27 мм Y& Y3 Y2 1П 113 т MSA HRS0 0VFL YO 7 77мм Рис. 18.7. Расположение элементов на кристалле АУО 340 Структура АУО была разделена на пять секций: 1) умножитель; 2) сумматоры, аккумуляторы с элементами выполнения специальных функций; 3) регистры общего назначения XL и YL; 4) адресные контроллеры (используются дважды); 5) регистры команды и управления. Каждая из секций обозначена на чертеже кристалла, их размеры можно сравнить. Для каждой секции, за исключением секции управления, использовалась одна и та же основная схема проектирования и компоновки. Каждая секция компоновалась на основе иерархического подхода, т. е. начиналась с вертикального соединения базовых логических ячеек для получения одноразрядного среза для конкретной функции. В каждом из разрядных срезов максимально использовалась возможная избыточность ячеек. Все разрядные срезы затем стыковались для образования -разрядной функции. При таком поразрядном подходе экономится значительная площадь кристалла и только шины данных, входящие и выходящие из функционального блока, растягивают секцию до размера, равного ширине шин. Например, шины XS и YS, входя в секцию сумматора-аккумулятора, требуют того, чтобы каждая из шин протягивалась вдоль каждого из разрядных срезов (с 0 до 16), даже если она никогда не потребуется для соединения с разрядным срезом 16. Напротив, шины Т, F, G, U, V, Н и W встроены внутрь секции, содержащей сумматор, аккумуляторы, логические элементы, и образуют связь между ячейками только по вертикальному срезу. Этот прием не только экономит площадь кристалла, но и устраняет паразитные эффекты монтажа, связанные с не очень рациональным подходом к компоновке, которые имели место при проектировании сумматоров как изолированных ячеек. Как представлено выше, тракты передачи данных для каждой секции разводились по вертикали для каждого разрядного среза и объединялись через иоликремний. Такое использование очень длинных поликремниевых проводников оказалось возможным благодаря низкому сопротивлению, обеспечиваемому силицид-платиновым технологическим процессом. В противном случае задержки в соединениях, связанные с применением высокорезистив-ного поликремния, стали бы чрезмерными и в проекте не была бы достигнута необходимая производительность прибора. Вертикальная разводка трактов передачи данных позволила выполнить соединения цепей питания, земли и быстродействующих сигналов управления горизонтально через разрядные срезы металлическими проводниками. Такой подход реализует преимущества микроКМОП-процесса, позволяющие использовать скрытые контакты. Внутренние выводы логических ячеек могут быть соединены в поликремнии, что позволяет таким образом выполнять разводку цепей управления и питания непосредственно в слое над активными приборами. Единственной секцией в проекте, которая компоновалась иначе, была секция логики управления и дешифрирования. Эта секция содержит регистр сдвига на 4 и регистры задержки командного конвейера, а также узел дешифрирования входов кода операции для получения конкретных управляющих сигналов. Эти схемы декодируют 78-разрядное слово микрокоманды в 184 управляющих сигнала. Данные 78 разрядов поступают с 20 выводов команды и принимаются за 4 такта (тактовая частота > 16 МГц) в течение одного системного цикла. Дешифрирование реализовано на уровне логических вентилей. Число элементов в схеме дешифрирования было минимизиро-вано; они были в основном представлены вентиляторами типа И - НЕ, буферными усилителями двух типов разных размеров, каждый из которых проектировался по критерию минимального времени задержки. Малые /длительности задержки потребовали соответствующих характеристик выходов регистров команды для согласования с большими емкостями линий управления, пересекающих каждую функциональную секцию. Ячейки для схем управления проектировались так, чтобы соединения выполнялись легко и основой подхода было построение рядов ячеек и междурядное соединение металлическими проводниками. Сводные характеристики компоновки прибора из табл. 18.2 подтверждают тот факт, что по плотности компоновки данный подход не очень эффективен. Однако при небольшом сроке разработки и высокой производительности результаты приемлемы. Рассматривались и другие методы дешифрации (программируемые логичес-кие матрицы, ПЗУ и т. п.), но они были отвергнуты на том основании, что производительность была важнее рациональной компоновки. Следующей проблемой компоновки была разводка цепей питания СБИС. В основе подхода было разделение цепей питания и земли элементов ввода-вывода от цепей питания и земли внутренних логических схем. Наличие сот-ни совместимых с уровнем ТТЛ выводов привело к использованию значительной части полезной площади для разводки цепей питания. Изоляция цепей питания была применена для устранения влияния на внутренние логичес-кие элементы периферийных приборов, которые могли бы вызвать всплески напряжения в системе питания. На кристалле расположено около 60 ТТЛ-драйверов, и это требует наличия шин питания системы ввода-вывода шири-ной 50,8 мкм для устранения миграции металла и падения напряжения. 18.7.4. Технические характеристики прибора В табл. 18.2 приведены характеристики топологии кристалла: общее число приборов, плотность компоновки, распределение площади кристалла между функциями. Предельная плотность компоновки СБИС невелика по сравне-нию с плотностью, которую мог бы обеспечить микроКМОП-процесс с разрешением 3 мкм. Однако, принимая во внимание размер кристалла, ограничен-ное время разработки и сложность архитектуры, такую плотность компонов-ки можно считать приемлемой по затратам на реализованную функцию. Разработка и компоновка кристалла были выполнены за 14 мес. В этот срок включена и итеративная фаза разработки архитектуры и конструирова-ния СБИС. Описанная здесь методология проектирования позволила выпол-нить задачу минимальным составом разработчиков. Для выполнения работы потребовались ведущий разработчик СБИС, чертежник и оператор автоматизированной системы машинной графики. Потребовался также еще один инженер на срок 5 мес. для логического моделирования. Архитектура системы разработана специальной группой инженеров. Для выполнения проектирова-ния базовой ячейки с конфигурацией, совместимой с общим планом кристал-342 ла, и проведения анализа временных характеристик ячейки была предпринята процедура детальной компоновки. Затем ячейка была прорисована при 1000-кратном увеличении чертежником проекта СБИС. Параметры ячейки были введены оператором в систему машинной графики типа С ALMA GDSII. Когда все ячейки для секции оказывались прорисованными, оператор должен был в интерактивном режиме соединить ячейки в срезы, а затем объединить срезы в законченную секцию с помощью системы машинной графики. По мере завершения чертежа каждой секции они интегрировались в конечную топологию кристалла. Такая система объединения ячеек, срезов, секций и кристалла в целом в интерактивном режиме для генерации шаблонов масок оказалась эффективной. В большинстве проектов заказных или полузаказных СБИС соединение этих частей выполняется вручную, а затем кодируется, что требует большего времени для компоновки. Интерактивное соединение при проектировании оказалось возможным благодаря скрупулезному планированию соединений на стадии планирования кристалла. В ходе проектирования потребовалась прорисовка около 50 ячеек и создание еще около 50 ячеек из исходного набора. Эти вторичные 50 ячеек были получены из первичных при незначительном редактировании оператором системы машинной графики и потребовались вследствие особенностей компоновки различных секций. Система С ALMA GDS II использовалась также для проверки правил проектирования шаблонов, подготовки данных для электростатического графопостроителя и подготовки лент для установки электронно-лучевой литографии. 18.8. ЗАКЛЮЧЕНИЕ В результате этой работы было продемонстрировано, что по микроКМОП-технологии с разрешением 3 мкм может быть построен современный арифметический процессор (для матричного процессора). Мы уверены, что данный прибор является представителем будущих СБИС-процессоров по следующим параметрам: 1)большая площадь отведена под шины; 2)большое число выводов. Эти параметры отражают необходимость разработки технологии, обеспечивающей большую плотность соединений, такой как двукратная металлизация, и более миниатюрных контактов. Отсюда также следует необходимость в дешевых многовыводных корпусах. Данная попытка демонстрирует возможность создания еще более мощных параллельных процессоров в одном полупроводниковом приборе по мере совершенствования технологии СБИС. Рассмотрение компоновки после ее завершения позволило более критически оценить данный подход к проектированию. На рис. 18.8 показана фотография кристалла. Установлено, что площадь кристалла полностью заказной СБИС, разработанной с тем же разрешением, составила 80% от площади, полученной в данном проекте. Однако это потребовало бы по меньшей мере 343 Рис. 18.8. Общий вид АУО трехкратного увеличения времени разработки. При использовании известных сегодня стандартных ячеек и автоматизированных способов размещения и разводки размеры кристалла превзошли бы те, которые можно реализовать. СПИСОК ЛИТЕРАТУРЫ [1] J. В. Bruckner, СЯ/-5 Micro-Programming Reference Manual, CHI Systems, Inc Goleta, Calif,, May 1982. [2] G. J. Culler, "Array Processor with Parallel Operations per Instruction" US Pat 4,287,566, Sept. 1,1981. [3] A. E. Charlesworth, "An Approach to Scientific Array Processing: The Architectural Design of the PP-120B/FPS-164 Family," Computer, 14{9):18-27 (Sept. 1981). [4] Ed Greenwood et al., "Array Processor Architecture Report," Rep. N00014-80-C-693-I Feb. 15,1982. [5] B. Fette and L. Hazelet, "Electronic Digital Adder," U.S. Pat. 3,843,876, Oct. 22,1974. [6] D. T. Fitzpatrick et al., "A RISCy Approach to VLSI," VLSI Des.y 4th Quarter 1981 pp. 14-20. ЦИФРОВАЯ ФИЛЬТРАЦИЯ В ЧАСТОТНОЙ ОБЛАСТИ ПРИ ИСПОЛЬЗОВАНИИ СБИС Е. Шварцландер, мл.1, Г. Холлнор2 19.1. ВВЕДЕНИЕ Технология СБИС и техника обработки сигналов развиваются в тесной взаимосвязи. Это обусловлено тем. что цифровая обработка сигналов традиционно требовала высоких уровней производительности при вычислениях. Преимуществом прикладных задач цифровой обработки сигналов (по технической реализации) является значительный объем вычислений, большинство операций которых не зависит от обрабатываемых данных. Поэтому для их реализации могут использоваться конвейерные или параллельные архитектуры. Важным аспектом наиболее полного использования технологии является четкое определение критериев оптимизации, которые меняются в зависимости от конкретной задачи (минимизация числа элементов, мощности, размеров, стоимости, типов элементов и т.д.). В этой главе основной целью является минимизация числа элементов, что требует максимизации числа операций на элемент, определяемого как произведение числа вентилей на тактовую частоту. Приблизительная зависимость этого параметра от тактовой частоты представлена на рис. 19.1. В настоящее время максимум достигается на тактовой частоте, примерно равной 10 МГц. Ниже этого значения плотность логических элементов ограничивается сложностью устройства, которая растет относительно медленно с уменьшением частоты. Для тактовой частоты выше 10 МГц плотность логических элементов довольно быстро уменьшается частично из-за превалирования интерфейсных схем ТТЛ, с которыми нелегко оперировать на частотах выше 10 МГц, а также из-за высокой потребляемой мощности существующих семейств быстродействующих логических элементов. Другой метод выбора технологии сводится к рассмотрению достижимого уровня сложности. Для большинства функций существует "критическая масса" логических элементов, необходимая для их реализации. При низком уровне логики заданная функция не может быть выполнена на одном кристалле и должна быть разделена на части для реализации либо на базе нескольких кристаллов (которые содержат дополнительные драйверы ввода-вывода, дополнительные выводы корпусов и т.д.), либо путем последовательного выполнения (которое потребует дополнительных управляющих логических цепей, изменяемой памяти и др.). В любом случае эффективность значительно увеличивается, если заданная функция реализуется полностью на одном кристалле. 1Отдел оборонных систем фирмы TRW, Редондо-Бич, Калифорния, 2Отдел оборонных систем фирмы TRW, Маклин, Виргиния. 0 ... 53 54 55 56 57 58 59 ... 78 |