Раздел: Документация

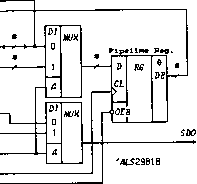

0 ... 98 99 100 101 102 103 104 ... 119 74ALS819 - 8-разрядный диагностическо-конвейерный регистр (Diagnostics/Pipeline Register, рис. 7.22,а), описываемый функциями SDO = QS7MV DS -М, Г QSruvnOE=DS-M = l, р„ * г \ Z-состояние при ОЕ = 0,r=i Уг Q5+ = JDrd# V QSrdH, Q+ = DBrdHL V QrdHL, г = 0... 7, где Do = DS-Лу DB0M, Dr = QSr-i~Mv DBrM, r = 1,2,..., 7; 74ЛХ529818, 74ЛС11818 - 8-разрядный диагностическо-конвейерный регистр (рис. 7.22,6), описываемый функциями SDO = QSjMM DS М, ( QSr при ОЕА = 1, DAr - < Z-состояние при ОЕА = 0, fgr при тжв = о, и и т = Z-состояние при ОЕВ = 1, Q5+ = DrdH\lQSrdH, Q+ = (ZUrM V QSrM) • <*Я£ V Q ДгЛ, г = 0,1,..., 7, Dq = DS Л V US DBqM V DS QSqM., DT - QST-{M V ~DS DBTM V DS QSTM, OEA = Q, Q+ = DS • M dH V Q dH~ (сигнал ОЕА представляет собой сигнал DS M, привязанный к тактовому сигналу Я). На структурных схемах описанных устройств (рис. 7.22) введены названия регистров: Shadow Reg. - теневой регистр, Pipeline Reg. - конвейерный регистр. Узел М2 в ИС 74ALS819 вычисляет контрольный разряд РЕ (Parity Even - четный паритет) - РЕ = 0 при нечетном числе разрядов Qr = 1 и РЕ = 1 при четном числе разрядов Qr = 1. Таким образом, по 9-разрядной шине PEQ7 .. .QiQq всегда передается нечетное число разрядов, равных I. Это свойство можно использовать при передаче данных для обнаружения однократных ошибок в параллельном канале связи. Режимы работы ИС 74ALS819 приведены в табл. 7.2. Интегральные схемы 74ЛХ5"29818 и 74ЛС11818 можно использовать в качестве приемопередатчиков с памятью, позволяющих производить некоторые преобразования данных внутри 0LSe\9 Д1£29в1в /£11818

22 21 20 19 IB 17 IS IS 1* 1%>CL DA 0 1 2 3 4 5 6 7 >c DS M 12 - GND, 2« - Vcc -4 RG <- RG SDO DA 0 1 2 3 4 5 6 7 К DS M >CL 1* -01 RG <- RG SDO 2 3 « s 10 11 12 13 DB- DS-M- D/l-DB- DS-M- m:- 3TS- 12 - Ш>,2« - Vcc s"9 " GM>, 21,22 - Vcc Рис. 7.21 Sh«%clov R«y.

Plp«lin« R«Q

M2 ►PE >QT-0 ►SDO /1LS819 ShmdovBey

Таблица 7.2. Режимы работы ИС 74ALS819

ИС. Режимы работы ИС 74ЛХ529818 и 74ЛС11818 приведены в табл. 7.3. На рис. 7.23 показаны двухступенчатые 8-разрядные сдвигающие регистры (Dual Rank 8-bit Shift Registers): 74ALS962 - ИС, описываемая функциями: DB = Г Qr при ОЕ = DISiDTSo = 1, т Z-состояние при ОЕ = О, Qt = DTdH V QTdH при DT = DBrTJlSj V QStDIStu V QTDISiDISTu, QS+ = DTdH V QSTdH при Do = DS DTSsDIStd V QoTJTStd V QS0DISSDISTD и DT = QT-XL4SsDISTD4Qr~DTSTDVQSTDISsDISTD, r = 0...7 (DISo - Output disable, DISi - Input disable, DIStu - Transfer up disable, DIStd - Transfer down disable, DISs - Shift disable); Таблица 7.3. Режимы работы ИС 74ALS29818 и 74ЛС11818

/1LS962 ALS963 ALS964

17 IS 13 14 1 3 12

16 13 14 13 12 RA

19 18 17 16 13 14 13 12 8 - GHD, 18 io - GHD, 20 - V Ю - GHD, 20 - V 74ЛХ5963 - ИС с синхронным сбросом регистров сигналом R, описываемая функциями: DB = Г Qr приО£С7 = 1, r 1 Z-состояние при ОЕ GI = О, Qt = DlrdHL V QrdHL, Dlr = DBrGI V QSrR GM V QrR Gl• GM, QS+ = D2rdH V QSrdH, r = 0 ... 7, D2,0 = DSRES- Ё~М V Q0R EM V QS0R-E~S EM, D2r = QSr-iR • ES Ё~М V QrR EM V QSrR • ES • Ё7И (GM, EM - разрешение передачи (Move) из регистра в регистр, GI - разрешение ввода с шины DB, ES - разрешение сдвига последовательных данных DS); 74ЛХ5964 - ИС с синхронным (R) и асинхронным (RA) сбросом регистров, отличающаяся от ИС 74ЛХ5963 только функциями: Qt = (DlrdH V QrdH) Ш, QS+ = (D2rdH V QSTdH) Ш. CO DB Н DJS0 DJSi

CAisaety als9b2 ► qs DB DJ awxf-1 l->CL B«q. 1 D q i-4е1 * г+60е db -, /1LS963 DJ awxf-2 B«q. 2 4>c rg d as qs7 qs7 CALS964) 5/й E 57DS E? Ей 7.2. Сдвигающие регистры PI/SO и PI/PO 615 Таблица 7.4. Режимы работы ИС 74ALS963

0 ... 98 99 100 101 102 103 104 ... 119 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||