Раздел: Документация

0 ... 97 98 99 100 101 102 103 ... 119 Таблица 7.1. Описание работы ИС 561ИР6

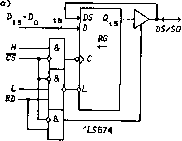

ние сигнала AS - 1 включает асинхронный режим приема и передачи). Данная ИС представляет собой приемопередатчик со сдвигающим регистром (см. § 5.9), который можно использовать и как приемопередатчик без памяти (при асинхронной загрузке). Приемопередатчик позволяет производить преобразование последовательных данных в параллельные, параллельных - в последовательные с коммутацией приемника и передатчика данных с помощью сигнала Т. Параллельный обмен данными между шинами DA и DB может выполняться с запоминанием данных в регистре. На рис. 7.15 приведены ИС: 7494 - 4-разрядный сдвигающий регистр типа PI/SO с асинхронными потенциальными установкой и сбросом, описываемый функциями: Q+ = STTV(DTdHvQTdH)-R, г = 0,1,2,3, D0 = DS, DT = QT-U г =1,2,3, где STT = SlrEx V S2tE2- 74X596 - 5-разрядный сдвигающий регистр типа PI/PO с асинхронными потенциальными установкой и сбросом, описываемый функциями (7.11) при STT = SrE; 74X99 - 4-разрядный сдвигающий регистр типа PI/PO с синхронной параллельной загрузкой данных и двумя тактовыми входами CL (Clock Load - тактовый сигнал для загрузки данных) и CS (Clock Shift - тактовый сигнал для сдвига данных), связанными функцией С - CS LVCL-L (можно исполь- (7.11) 94

JLS96 12 - ега.з - 179

а - GHD,16 - v 16

D 2 ii hs я? i £.99 Rfi L hCL >CS JS KS 178 Q3 a3 12 - GHD.s GNU, 3 199 DD L5674 7 9 20 тт 11

-<L 4 -Q 11 20 21 22 23 12 " GHb, 24 - V L H M RD Rfi DS >S0 Rfi 7 - GND.n - V- T676 -Ids RG 11 . 12 - GHD,2* - 12 - GHD,29 HC HC Рис. 7.15

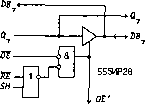

зовать один тактовый сигнал CS = CL = Я); ИС описывается функциями: Qt = DTTd(CS -LVCL-L)V QTdCS -LvCL-L, г = 0,1,2,3, DT0 = (Q0JS V Q0KS)LV D0L, DTT = QT-\L V DTL, r = 1,2,3; 74178- 4-разрядный сдвигающий регистр типа PI/PO с синхронной параллельной загрузкой данных, описываемый функциями: Q+ = DTTdH V QTdH, г = 0,1,2,3, DTq = QqSH Г/ V DqSH • L V DS SЯ, 1(7.12) DTT = QTSH -Iv Dr~SH -LM Qr-iSH, J где г = 1,2,3, L (Load) - загрузка, 5Я (Shift) - сдвиг (вход 5 Я имеет приоритет по отношению ко входу L); 74179- 4-разрядный сдвигающий регистр типа PI/PO с синхронной параллельной загрузкой данных и асинхронным потенциальным сигналом R сброса регистра в нулевое состояние, описываемый функциями (7.12) при Qt = (DTTdH V QrdH) R, г = 0,1,2,3; 74199 - 8-разрядный сдвигающий регистр типа PI/PO с синхронной параллельной загрузкой данных, асинхронным потенциальным сигналом R сброса регистра в нулевое состоя-ние и входами последовательного ввода данных JS и IiS (при JS = КS получается вход DS); ИС описывается функциями (7.5) при Я = Я1Я2; 74Т,5674 - 16-разрядный сдвигающий регистр типа PI/SO с синхронной загрузкой и двунаправленным последовательным входом/выходом DS/SO (рис. 7.16,а); 74F676 - 16-разрядный сдвигающий регистр типа PI/SO с синхронной загрузкой и раздельными последовательными входом DS и выходом SO (рис. 7.16,6). Сдвигающие регистры с расширением знака. На рис. 7.17 показан сдвигающий регистр типа PI/PO с расширением знака и синхронной параллельной загрузкой данных (ИС 555ИР28 и 533ИР28): DS0, DSi - мультиплексные последовательные входы, управляемые адресным сигналом A; SE (Sign Extension) - расширение знака; RE (Register Enable) - разрешение регистра (разрешение операций сдвига и загрузки); SH (Shift) - сдвиг, SO = Q7 - последовательный выход; 555ИР2В 533ИР2В ТУ 0 1 д >SE RE SH OE RG 0.7 14 2 7 13 11 DS 0 1 A SE >C R£ SH OE RG 0.7 10 - GHD, 20 12 - GHD, 24 - Vc 3,10,13,15 - HC  Рис. 7.17 Рис. 7.18 DB7.. .DBiDBq (Data Bidirectional) - двунаправленный параллельный вход/выход. Работа ИС описывается функциями: DOT QT при (REV SH) ОЕ = 1, Z-состояние при (же У SH) • ОЕ = 0, Qt = (D\dHvQrW)-R, г = 0,1,...,7, Do = (DS0A SE V DS\A SE V Q0SE) -RE-SHv VDB0RE ~SH V QqRE, DT = QT XRE SH V DBTRE S~H V QT~RE, r = 1,2,..., 7. Из этих соотношений следует, что при же = SH = 0 производится загрузка данных (DT = DBT и параллельный выход находится в Z-состоянии), при же = 0 и SH = 1 - ввод данных по последовательному каналу (Dq = DSi при же = 1 и Рт = Qr-i, г = 1,2,..., 7) или расширение знака (D0 = Q0 при SE = 0 и DT = Qr-i, г = 1,2,. ..,7) и при же = 1 - хранение данных (Dr = Qr-i, г = 0,1,..., 7). При выполнении операции расширения знака в триггер Q0 записывается знаковый разряд и затем производится его сдвиг в заданное (необходимое) число разрядов без изменения содержимого триггера Q0 для нормирования размера разрядной сетки чисел, представленных в дополнительном коде. Например, числа +5 и -5 при разных размерах разрядной сетки могут иметь представления: 0.10 1,1.0 11, 0.0 0 0 1 0 1,1.1 1 1 0 1 1, 0.0 0 0 0 0 1 0 1, 1.1 1 1 1 1 0 1 1. Схема управления Z-состоянием выходов DBT в ИС 555ИР28 изображена на рис. 7.18. Сигнал ОЕ = (REV SH)OE подается на остальные вентили с Z-состоянием выхода. Сдвигающие регистры с входным регистром памяти. Регистр памяти можно включить как на параллельном выходе сдвигающего регистра (см. § 7.1), так и на его параллельном входе. Получаемые таким способом устройства обладают большими функциональными возможностями, чем каждый из используемых узлов в отдельности. На рис. 7.19 представлены 8-разрядные устройства с асинхронной потенциальной загрузкой данных в сдвигающий регистр: 74ЯС589 - устройство на основе сдвигающего регистра типа PI/SO (рис. 7.20,а), описываемого функциями (7.9); 74X5597 - устройство на основе сдвигающего регистра типа PI/SO с асинхронным потенциальным сбросом сигналом R (рис. 7.20,6), описываемый функциями SO = Q7 и Q+ = [DTL V (DTTdH V QTdH) X] • R, г = 0,1,..., 7, DT0 = DS, DTT = gr b r = 1,2,..., 7; (7.13) 74X5598 - устройство на основе сдвигающего регистра типа PI/PO с асинхронным потенциальным сбросом сигналом R (рис. 7.20,б), описываемый функциями (7.13) при DT0 = DSoAV DSXA, SO = Q7 w DB =[ °-r при 0E ° T \ Z-состояние при OE = 1. Во всех перечисленных ИС используются синхронные регистры памяти. В ИС 74X5598 сигнал CEN (Clock Enable) служит для включения (CEN = 0) и выключения (CEN = 1) тактового сигнала Н (см. рис. 7.20,в). Действительно, упрощенным методом анализа, изложенным в § 2.4, можно получить: а+ = НаСШмН = Я V а • C~EN, а значит тактовый сигнал а+ = Н при значении управляющего сигнала CEN = 0 и а+ = Я V а при значении CEN = 1. При первом изменении сигнала Я с 1 на 0 установится значение а = 1, поэтому а+ = 1 при всех дальнейших изменениях сигнала Я, если значение управляющего сигнала CEN = 1. Многофункциональные устройства на основе сдвигающих регистров. На рис. 7.21 показаны ИС: D □ 1 z з 4 5 6 7 НС589 S6 ДО >с ОЕ SO D О 1 г 3 4 5 6 7 LSS97 S6 ДО - >с DS SO ЯZ z >CL я 1>с DS, от i LSS98 SG RG OE 3 4 5 6 7 \-DS SO -SO GHD, is CO Z-

Я-DS- 01- HC589 s - GHD, is - V. Рис. 7.19 10 - GHD, 20 - V

Z- H-DS-

LS597

в) DB+- tx-z- ff- Jf- RG LS598

so so - i,,- 0 ... 97 98 99 100 101 102 103 ... 119 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||