Раздел: Документация

0 ... 75 76 77 78 79 80 81 ... 119 соотношением Qt = (ATL V QTL) R, где г - номер триггера в адресном регистре (Vdd = +15 В, Vee = -15 В); 591KII2 - двухразрядный MUX-DMUX 8 -> 1/1 -► 8 (Vdd = +15 В, Ке£ = -15 В); 591КНЗ - MUX-DMUX 16 1/1 16 (Vdd = +15 В, Veb = -15 В). Ключи 590КН10 характеризуются малой амплитудой выбросов напряжения на аналоговых выходах при изменении управляющего сигнала, а ключи 590КН13 - высоким быстродействием. Основные параметры аналоговых ключей и мультиплек-соров-демультиплексоров серий 590 и 591 приведены в табл. 6.9 (toN - время включения, /dd - ток потребления от источника питания Vdd или Vcc)- 6.6. Шифраторы Дешифраторы (6.1) являются преобразователями двоичного п-рачрядного кода в унитарный 2"-разрядный код. все разряды которого, за исключением одного, равны нулю. Шифраторы выполняют обратное преобразование, т.е. на вход шифратора подастся унитарный код. а на выходе получается соответствующий двоичный код. Первые четыре строки габл. 6.10 описывают шифратор, выполняющий преобразование 4-разрядного унитарного кода /3/2/1/0 в двухразрядный двоичный код АуА0. Для шифраторов должно выполняться условие /, • Ij = 0 при i ф j. Таблица 6.10. Приоритетный шифратор 4x2

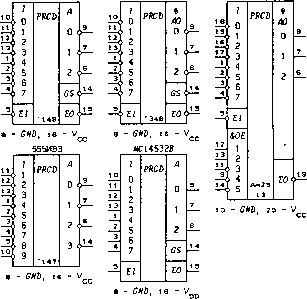

Если сигналы на входы 1{ поступают от независимых источников, то это условие невыполнимо. В этом случае каждому входу назначается свой приоритет. Будем считать, что чем больше номер входа г, тем выше его приоритет. Шифратор должен выдавать двоичный код числа г, если I{ = 1, а на все входы Ij, имеющие больший приоритет, поданы нули. Такие шифраторы называются приоритетными шифраторами (PRCD). Табл. 6.10 задает приоритетный шифратор 4 х 2. Приоритетные шифраторы. Приоритетные шифраторы используются для построения шифраторов клавиатуры, контроллеров прерываний для микроЭВМ и т.п. Функционирование приоритетного шифратора 8x3 555ИВ1 (рис. 6.58) описывается табл. 6.11. Входные и выходные сигналы шифратора имеют назначение: EI (Enable Input) - сигнал включения шифратора, GS (Group Signal) - сигнал, говорящий о наличии хотя бы одного возбужденного входа /, при включенном состоянии шифратора (GS = 1 при /, = 1 хотя бы для одного i при Е1=1), ЕО (Enable Output) - выходной сигнал разрешения, указывающий на отсутствие возбужденных входов /, при включенном состоянии шифратора (ЕО = 1 при EI = 1 и /,; = 0 для всех г), A2,Ai,Aq - три разряда выходного двоичного кода. Сигналы EI и ЕО предназначены для каскадирования приоритетных шифраторов. Понятно, что двоичный код А = А2А] А0 можно считывать только при значении сигнала GS = 1 (сигнал GS может быть использован в микроЭВМ для запроса прерываний по вектору /1). Непосредственная построчная запись значений функций по табл. 6.11 дает: 777 GS = EI\J /„ ЕО = Е1\~[7и A2 = El\j /„ GS=EI-EO, :=0»=0»=4 A\ = EI • (I7 V 77/6 V /7/6/5/4/3 V /7/6/5/4/3/2),(6 13) A0 = EI- (/7 V7776/5 V /7/6/5/4/3 V /7/6/5/4/3/2/1). Функции Ai и Aq на основании тождеств (1.32) могут быть упрощены: Ai = EI (I7 V /6 V /5/4/3 V /5/4/2), Ао = El • (/7 v 76/5 v77767574/з v 777б75747з72/1). Проведенный синтез приоритетного шифратора позволяет глубже понять функции, им выполняемые. Все выпускаемые в 555ИВ1555ИВ21804ВРЗ  Рис. 6.58 Таблица 6.11. Приоритетный шифратор 8X3 555ИВ1

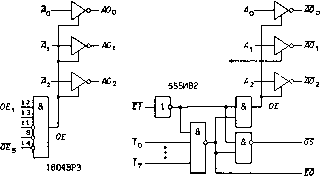

интегральном исполнении приоритетные шифраторы 8x3 строятся на основании полученных функций. На рис. 6.58 приведены ИС: 555ИВ1, МСТ4532/?- приоритетные шифраторы 8x3, выполняющие функции (6.13); 555ИВ2 - приоритетный шифратор 8 X 3 с Z-состоянием выходов разрядов двоичного кода; 555ИВЗ - приоритетный шифратор 10 X 4; 1804ВРЗ - приоритетный шифратор 8 X 3 с Z-состоянием выходов разрядов двоичного кода. У шифратора 555ИВ1 все входы и выходы инверсные по отношению к указанным в табл. 6.11, т.е. активные уровни этих сигналов равны 0. Реализация выходов с Z-состоянием ИС 1804ВР1 и 555ИВ2 представлена на рис. 6.59: ОЕ = OEiOE2OE3OE4OE5 - для ИС 1804ВРЗ, ОЕ= EI - \J U - для ИС 555ИВ2. t=0  Рис. 6.59 Функционирование приоритетного шифратора 10 х 4 555ИВЗ описывается табл. 6.12. Как и для предыдущего шифратора, по табл. 6.12 с помощью построчной записи значений функций и последующей их минимизации на основании тождеств (1.32) можно получить: А3 = h V /8, А2 = I9I8(I7 V h V h V I4), Ai = hh(hy h V /5/4/3 V /5/4/2), Л0 = /9 V 7978(/7 V 76/5 V /6/4/3 V /6/4/2/1) Таблица 6.12. Приоритетный шифратор 10x4 555ИВЗ

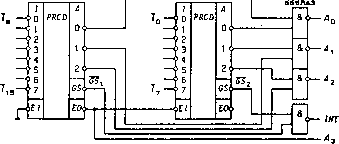

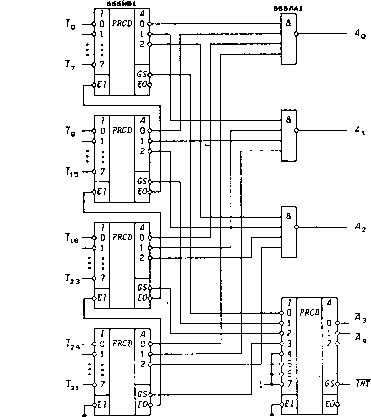

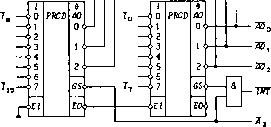

(в принципе в выражении для функции Aq переменную /9 можно исключить). Каскадирование приоритетных шифраторов. На рис. 6.60 показана схема приоритетного шифратора 16 X 4 (наивысший приоритет имеет вход /15). Верхний шифратор включается только в том случае, если не возбужден ни один из входов Ii нижнего шифратора (все /, = 1). Четвертый разряд А3 двоичного числа может быть снят также с выхода GS верхнего шифратора. Логические элементы И-НЕ выполняют функцию ИЛИ для сигналов Aj 11 GS двух шифраторов. Так, например, сигнал INT = GSXGS2 = GSi V GS2 (INT = 1 только в том случае, если возбужден хотя бы один вход 10 - /]5; INT - Interrupt Request- запрос прерывания).   Рис. 6.61 555ИВ2  0 ... 75 76 77 78 79 80 81 ... 119 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||