Раздел: Документация

0 ... 77 78 79 80 81 82 83 ... 119 ALSS16 ALSS19 ALSSZO

Ш), 20 - /1LS522 Ш), 20 - ALSsaa

11 1 3 16 18 <?м>, АС\ 1 20 520 .ALS521 /I О 1 г з 4 5 Б 7 ~ЗГ 0 1 2 3 4 5 Б 7

10 - см), 20 ALSEB3 - 4 ю - GNU, 20 - V «11521 (нет 3) 5 - GNU, 15 - V Для каскадирования компараторов с инверсными выходами можно использовать вход стробирования Е. Пусть, например, два 8-разрядных компаратора в соответствии с (6.15) выполняют функции: F, = Е, 114 р=0 15 ВР, Е2 я2 • пч р=8 в„ Тогда, положив Е\ = Е и Е2 = Е, получим: 71515 F2 = Е П ЛрФЯр • П лр©Яр = Ё П лр® бр р=0 р=8 р=0 Рассмотренному методу каскадирования цифровых компараторов соответствует схема с их последовательным включением в отличие от параллельного включения, показанного на рис. 6.69. Каскадирование m компараторов осуществляется на основании соотношений: Е\ = Е и Ej - Fj-i (j = 2,3,...,m), что дает схему с последовательным включением тп компараторов (рис. 6.71; тп = 4). Для каскадирования компараторов, имеющих прямой открытый коллекторный выход, можно использовать параллельное их включение, подобное показанному на рис. 6.69.

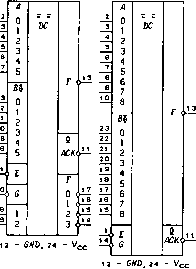

TL В16-2 П- гг Рис. 6.71 Выпускаются ИС, содержащие цифровой компаратор и дешифратор, который включается только при равенстве кодов, подаваемых на компаратор, или компаратор и некоторые схемы, вырабатывающие дополнительные управляющие сигналы. На рис. 6.72 показаны такие ИС: 74ALS29806 - 6-разрядный компаратор с управляемым дешифратором 2x4, выполняющий функции 5 Г = Е П Ар © Вр, АСК = EG, F{ = F х\2ху, i = е2ех Р=о (АСК - Acknowledge - подтверждение); dLS29B06 /U.S29809  ACKQ Г Г-О G АСК< Г 3~ Рис. 6.72 Рис. 6.73 74Л/,529809 - 9-разрядный компаратор с управляющим сигналом подтверждения (АСК), выполняющий функции 8 F = Е Л Ар 0 Вр, АСК = F G. р=° Каскадирование ИС 74Л 529806 показано на рис. 6.73. Данная схема выполняет функции п F= II Арф Вр, АСК = F - G, F,= F-xe22x\\ i = е2е1. р=0 При каскадировании можно последовательно включать любое число ИС для увеличения разрядности сравниваемых кодов. Программируемые цифровые компараторы. Для сравнения двух n-разрядных кодов компаратор должен иметь не менее 2п входов. Из-за ограничений на число выводов ИС приходится принимать п < 9. Если один из кодов предварительно записать в ИС, то потребуется только п входов для подачи другого кода. Запись кода в ИС можно производить пережиганием плавких перемычек при программировании ИС. Выпускаемые в интегральном исполнении программируемые цифровые компараторы (Fuse-Programmable Identity Comparator) представлены /1LSS26 ALSSZ7 ALSSZB /ILS8I2 -л

ю - GND.20 - Vc

8 - GHD, ie

ACK6H 12 - GND, 24 io - GND,20 - Vc Рис. 6.74 на рис. 6.74: 74Л 5526 - 16-разрядный компаратор с программированием 16 разрядов кода В, выполняющий функцию 15 F = Е • П Ар 0 FBp, р=0 где FBp - запрограммированные разряды кода В; 74Л 5527 - 12-разрядный компаратор с программированием только 8 младших разрядов кода В, выполняющий функцию 711 F = Е • П ар © fbp IIap® в р=0р=8 где FBp - запрограммированные разряды кода В; 74Л 5528 - 12-разрядный компаратор с программированием 12 разрядов кода В, выполняющий функцию и F = Е J] Ар © FBp, р=0 где FBp - запрограммированные разряды кода В; 74Л 5812 - 12-разрядный компаратор с управляемым де- шифратором 2x4, выполняющий функции ii F = Е J] Ар © FBP, АСК = F-G, F = F- хх, i = е2е„ р=0 где FBp - запрограммированные разряды кода В (АСК - Acknowledge). а) Programming Circuit Blown - О Intact - 1 пЕг Programming Circuit Blown - 0 /ntact = 1 Programming Enable Circuit alsszb CuLSSZB) = 1 =1 {7}J Test;Test Test Blow fuse Verify Verify.Verify у Рис. 6.75 Функциональная схема программируемых компараторов 74 Л/,5526 и 74Л 5528 показана на рис. 6.75,«. При программировании кода В он подается на выводы Aj (Aj = FB:). При пережигании (Blown) перемычки программируется значение FBj = 0. Временные диаграммы, определяющие алгоритм программирования, изображены на рис. 6.75,6 (уровни напряжений входных сигналов Vjh = 2...5,5 В, Уц = 0...0,8 В, Viffff = 11,5... 12,5 В; напряжение источника питания Vcc - 6,5... 7,5 В и длительность импульса программирования tw = 10... 50 мкс). Перемычки должны пережигаться по одной последовательно во времени. Потребляемый по программируемому входу Aj - FBj ток Iihh < Ю МА, а по входу управления Ё-1шн < 1,24 мА. Адресные компараторы. Комбинационные схемы, имею-N < 2" информационных Aj и п управляющих Рр щие 2"-1 Таблица 6.13. 16-разрядный адресный компаратор

Рис 6.76 0 ... 77 78 79 80 81 82 83 ... 119 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||