Раздел: Документация

0 ... 76 77 78 79 80 81 82 ... 119 j J г-4£7

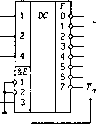

7 bEI PRCD AO ► аэ0 ►ДО, roj-«- l А-»- Jlrpr тяг Рис. 6.63

Инверсный унитарный код е\ТеТ3ТТэТ2Т,Т0 Рис. 6.64  Рис. 6.65 а) 278

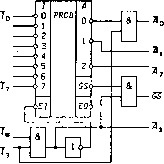

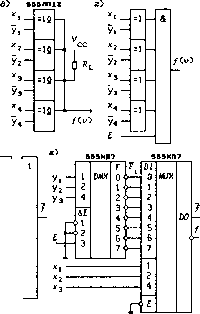

7 - GHD, 14 - V 3-0 4 fft L D El OEi- 7-4 4 L D 4 bEI 0E6-h>EI OEi L D f -i . 4 Г4 " Г7 Унитарный код FttFt0Fe r,r0 Г"» с Г ис o.oo На рис. 6.61 показана схема приоритетного шифратора 32 х 5 (наивысший приоритет имеет вход /31)1 которая может быть расширена до схемы приоритетного шифратора 64 X 6 добавлением еще четырех ИС 155ИВ1 и заменой 4-входовых ЛЭ И-НЕ на 8-входовые. Приоритетный шифратор 8 x 3 555ИВ2 имеет выходы Aj с тремя состояниями, что позволяет использовать при каскадировании этих ИС функцию монтажное ИЛИ, исключив тем самым ЛЭ И-НЕ (рис. 6.62). Приоритетный шифратор 1804ВРЗ разработан для расширения контроллеров прерывания, используемых в микроЭВМ, построенных на базе микропрограммируемых секционных (раз-рядно-модульных) микропроцессоров серии 1804 [46]. Однако их можно использовать и для других целей, например в шифраторах клавиатуры. На рис. 6.63 показан способ каскадирования приоритетных шифраторов 1804ВРЗ. Применения приоритетных шифраторов. Одним из важных приложений приоритетных шифраторов является построение на их основе преобразователей произвольного п-раз-рядного кода в п-разрядный унитарный код. Схема преобразователя произвольного 8-разрядного кода, для разрядов которого установлены определенные уровни приоритетов, в 8-разрядный унитарный код показана на рис. 6.64. Шифратор 555ИВ1 преобразует произвольный код IrIe...I0 в двоичный 3-разрядный код, а дешифратор 3x8 (ИС 555ИД7) преобразует этот код в инверсный унитарный код FjFe • • Ко- Такие преобразователи используются в контроллерах системных шин микропроцессорных систем. На рис. 6.65 показано преобразование приоритетного шифратора 3 X 8 в приоритетный шифратор 4 х 10. Приоритетные регистры памяти могут быть построены на основе асинхронного потенциального регистра памяти и приоритетного шифратора. Приоритетный 4-разрядный регистр памяти 74278 (рис. 6.66,а) описывается функциями Q+ = DTL VQTL, ЕО = EI • Q3Q2Q1Q01 *Ъ = EF Q0, F\ = EI • QtQo, F2 = EI- Q2Q1Qo, F3 = EI- Q3Q2QiQ0, где r = 0,1,2, 3. Сигналы EI и ЕО предназначены для каскадирования приоритетных регистров памяти. Принцип каскадирования приоритетных регистров памяти показан на рис. 6.66,6". Приведенная схема представляет собой преобразователь произвольного кода D\\D\q ... D0 в прямой унитапнктй кптт Р.,Fr. J - - -1- - V. - 11 IU 1 - U* 6.7. Цифровые компараторы Пусть заданы две совокупности переменных v = (xn,...,xp,...,xi) и u" = (yn,...,yp,...,yi). Так как хр = 0 или 1 и ур = 0 или 1, то каждая из совокупностей переменных v и и" имеет по 2" комбинаций значений. Для краткости такие совокупности значений переменных принято называть кодами, а величины хр н ур - разрядами кодов. Комбинационная схема, реализующая функцию f(i/) = f(v,i>"), где v = (хп,..., xi, уп,..., j/i), которая равна 1 только при хр = ур для всех р = 1,2, ...,7i, называется га-разрядным цифровым компаратором, или схемой равнозначности кодов. Разряды хр и ур равны только в том случае, если хр@ур = 1, поэтому функция ппп /И = ПК © Ур) = П хр ® Ур = V хр ® ур (6л4) p=ip=i р-1 принимает значение, равное 1, только при попарном равенстве всех одноименных разрядов кодов. На рис. 6.67,а,б показаны две схемы, реализующие функцию f(v), которые построены для га = 4 на основании полученного выражения. Цифровой компаратор значительно упрощается при использовании ЛЭ сумма по модулю два с открытым коллекторным выходом (рис. 0.67.б), позволяющих реализовать функцию "монтажное И" для высоких уровней выходных сигналов ЛЭ. На рис. 6.67,г показан стробируемый 4-разрядный компаратор, выполняющий функцию- 4 /И = е П хр ® %» Р=1 где Е (Enable) - стробирующий сигнал.- Сигнал управления Е можно использовать как для блокирования (выключения) функции сравнения, так и для каскадирования компараторов (рис. 6.67,<)). На рис. 6.67,е изображен каскадируемый компаратор, полученный на основе схемы, показанной на рис. 6.67,6 (при каскадировании выход / одного компаратора подается на вход Е другого компаратора; таким способом последовательно можно соединять любое число компараторов). Стробируемый те-разрядный компаратор можно построить ill лпшг П1 тнп TTrti/rin 1 i. *упи ir п i тч п ч лиГ>ь О, 1 1-1 -..-, тх ДСга j Jib » niuiCnv/j/t- jl r id x\ ivij >/ib i xi iiiyit .IV v-(J* ; A. nd nL> a)

y. - X2. f<v> y2-Уз- *4. У4-

Рис. 6.67 6.67,э/с изображена КС, описываемая функцией 77 /(„) = DO = V Ш.-А» = V №И, i=0«=0 где v - (х3,Х2,Xi) - адресные сигналы каналов мультиплексора, Ki(u) = ххх, i - еееу - адрес канала, Е{ - EVyVvV- а этом основании легко показать, что КС выполняет функцию 7 /(i/) = Е V yfyylxxxX1 = Е хТ@УзхТ®У2~®У1, т. е. КС представляет собою 3-разрядный стробируемый компаратор. Действительно, на основании свойств первичных термов и минтермов функция  7 V хххт1 = 1 при Е = 1 и ур = хр для р = 1,2,3, 1=0 31 Пухальска! Г. И , Но»ос<льае»а Т. Я. что совпадает с общим определением цифрового компаратора. Цифровые компараторы. Выпускаемые в интегральном исполнении компараторы описываются функциями (6.14) при п > 6. На рис. 6.68 представлены ИС: 559СК1 - 8-разрядный цифровой компаратор, выполняющий функцию 7 F= \J(Ap@Bp) р=0 (tpd = 25 нс, Iol = 70 мА, 1СС = 130 мА); 559СК2 - 6-разрядный цифровой компаратор с фиксацией результата сравнения в асинхронном потенциальном триггере, описываемый функциями ~5 F = V (Ар © Вр), Q+ = F L V Q L [tpd - 45 нс по входам Л, tpd = 30 нс по входам В и L, Iol = 16 мА, Ice = 74 мА). S59CK1 559CK2

в - GND, is io-GM),20-Vcc,n -NC Выходы цифровых компараторов с открытым коллектором облегчают их каскадирование. На рис. 6.69 показан 18-разрядный цифровой компаратор с фиксацией результата сравнения в триггере Q. При значении сигнала загрузки L = 0 выход Q - F, т.е. получается обычный компаратор без фиксации результата. х,- 5 Уо У1 - Ув Ут

42 . *13- У12. У13- У17-j> Рис. 6.69 На рис. 6.70 приведены цифровые компараторы со строби-рующим входом Е: 74.4X5518 - 8-разрядный компаратор с прямым открытым коллекторным выходом и внутренними резисторами R = 20 кОм на входах Вр, подключенными к питанию Vcc (знак "ф" указывает задание высокого уровня сигнала на входах); 74ALS519 - 8-разрядный компаратор с прямым открытым коллекторным выходом; 74ЛХ5520, 74ЛС11520 - 8-разрядные компараторы с инверсным выходом и внутренними резисторами R = 20 кОм на входах Бр, подключенными к питанию Vcc] 74Л15521, 74Л2,5688, 74ЛС11521 - 8-разрядные компараторы с инверсным выходом; 74Л2,5522 - 8-разрядный компаратор с инверсным открытым коллекторным выходом и внутренними резисторами R - 20 кОм на входах 2?р, подключенными к питанию Vcc) 74Л2,5689 - 8-разрядный компаратор с инверсным открытым коллекторным выходом. Все перечисленные компараторы описываются функцией 7 F = ЕЦАр®Вр,(6.15) Р=о где Е - стробирующий сигнал. Входы Вр компараторов с внутренними резисторами можно подключать к переключателям, выключенному состоянию которых соответствует подача на входы Вр уровня сигнала логической 1. Это позволяет не ставить на входах компаратора внешние резисторы. 0 ... 76 77 78 79 80 81 82 ... 119 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||