Раздел: Документация

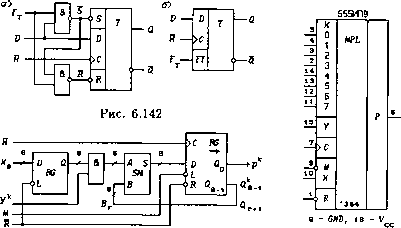

0 ... 92 93 94 95 96 97 98 ... 119 знаком, то произведение выдается в дополнительном коде. Округление результата умножения производится при подаче сигнала RND = 1. Значение сигнала RND записывается в D-триггер импульсным сигналом dCx V Су = CydCx VC*xdCY, т. е. перепадом любого из тактовых сигналов, при условии, что другой равен 0. Если этот триггер находится в состоянии Q = 1, то в разряд pii добавляется единица (число 211). Присвоение знака младшей части произведения рп - ро производится по сигналу RS = 0. Такое присвоение следует использовать только при умножении чисел со знаком (ТСх = 1, ТСу = 1). В этом случае модуль произведения представляется 22-разрядным числом р2\ - Ро, а знак фиксируется в разряде P22- Результат умножения для чисел со знаком представляется в дополнительном коде и присвоение знака младшей группе разрядов производится с помощью сдвигающего устройства SU по правилу: -:-1 Р23 *- Р22 *- * * • *- Р12 <- РИРЮРЭ • • • РО (знаковый разряд р22 поступает в старший разряд рц младшей группы разрядов произведения и в разряд ргз)- Значение сигнала Ft = 1 переводит регистры памяти произведения в прозрачный режим работы, при котором любые изменения информационных сигналов D сразу же передаются на выход (сигнал Fj = 1 блокирует действия тактовых сигналов Сг, и См)- Прозрачные £>-триггеры могут быть выполнены на основе /J/.R-5-триггеров, описываемых функцией переходов Q+ = S V (DdH V QdH) ~R. Если положить S = D • FT и R = D FtFt (RS = 0), то функция переходов будет иметь вид: Q+ = D-FTV (DdH V QdH) D FTFT. (6.62) Из этой функции следует, что при Ft = 1 значение Q+ = D не зависит от тактового сигнала. На рис. 6.142,а показана структурная схема прозрачного D-триггера, выполненная в соответствии с (6.62), а на рис. 6.142,6"- его условное обозначение. Выходы произведения с тремя состояниями позволяют подключать их непосредственно к системной шине данных микроЭВМ, т.е. умножитель можно использовать в качестве внешнего устройства для ускорения вычислений. Наличие входных и выходных регистров дает возможность использовать умножитель в конвейерных устройствах обработки данных. Выпуска-  Рис. 6.143Рис. 6.144 ются также БИС умножителей 1802ВРЗ (MPY-8) - умножитель 8x8 разрядов и 1802ВР5 (МРУ-16 фирмы TRW) - умножитель 16 X 16 разрядов [26, 27]. Последовательные умножители. В последовательных умножителях, вычисляющих n+m-разрядное произведение Р = Хп X Уто, где Хп - z„ i • • • хгх0, Ym = j/TO i ... j/i г/о, n-разрядное множимое Хп записывается во внутренний регистр памяти умножителя, а разряды множителя Ут подаются на умножитель последовательно, начиная с младшего разряда. Из традиционного алгоритма умножения чисел следует, что умножитель должен содержать накапливающий сумматор, состоящий из n-разрядного двоичного комбинационного сумматора и сдвигающего регистра, одновременно используемого в качестве аккумулятора старших разрядов суммы (рис. 6.143; п = 8). Регистр памяти числа Х8 построен на асинхронных потенциальных D-i-триггерах, а 9-разрядный сдвигающий регистр - на D-L/Д-тригтерах. Загрузка множимого As производится сигналом L = R = 0, который одновременно сбрасывает в 0 сдвигающий регистр. Умножение числа Хп на один разряд ук (к - номер разряда и номер такта) множителя Ут производится набором из п ЛЭ И: х; • ук = х, х ук. Пока поступают разряды множителя ук, сдвигающий регистр работает в режиме синхронной загрузки (М = 0). Эффект сдвига при загрузке по- Таблица 6.31. Последовательный умножитель

лучается за счет подачи разрядов аккумулятора Qr+i с весом 2Г+1 на входы сумматора Вт с весом 2Г (г = 0,1,...,7). Пример вычисления произведения Xs х Кб = 181 х 43 = 7783 = 2124-2U + 210 + 29 + 26-1-25-(-22+21 +2° представлен в табл. 6.31. Умножение выполняется за п + тп = 14 тактов с представлением 14-разрядного произведения Р в последовательном коде на выходе младшего разряда Q§ = р* сдвигающего регистра. Сигнал М производит переключение сдвигающего регистра с режима синхронной загрузки в режим сдвига (тп тактов производится загрузка чисел с выхода сумматора и п тактов - сдвиг для выдачи старших разрядов произведения). Число Ym может иметь произвольную разрядность. Последовательный умножитель 8x1 бит 555ИП9, построенный по рассмотренному принципу, показан на рис. 6.144. 6.14. Конвейерные устройства Реализация переключательных функций двухъярусными КС приводит к большим аппаратным затратам, что при сложных функциях практически не оправдано. Снизить аппаратные затраты (число ЛЭ) можно использованием скобочных форм функций, которым соответствуют многоярусные КС. Однако такой способ реализации переключательных функций приводит к значительному снижению быстродействия КС. Принцип построения конвейерных устройств. Скорость преобразования однотипной информации многоярусными КС (рис. 6.145) можно значительно увеличить с помощью конвейерной передачи информации от яруса к ярусу (рис. 6.146). В конвейерных устройствах между ярусами КС устанавливаются регистры памяти (РП), которые могут выполняться как на асинхронных потенциальных, так и на синхронных триггерах. Если на рис. 6.145 входные сигналы хр (р = 1,2,..., щ) не должны изменяться пока входные сигналы /, (q - l,2,...,ns) не примут истинных значений (пока во всей схеме не закончится переходной процесс), то в конвейерном устройстве на рис. 6.146 входные сигналы хр можно изменять сразу же после фиксации в регистре памяти значений выходных сигналов первого яруса КС. Фиксация выходных сигналов каждого яруса КС производится по окончании переходного процесса в ярусе с наибольшим временем задержки сигналов.

Рис. 6.145

Рис. 6.146 На рис. 6.147 показан сигнал L (Load- загрузка) асинхронной потенциальной загрузки информации в РП. Для достижения максимального быстродействия длительность Т\ сигнала Ь = 1 должна быть как можно меньше, но Достаточна для надежного срабатывания триггеров. Входные сигналы триггеров на интервале Тг не должны изменяться. Из этого следует, ;Пто минимальная задержка сигналов в каждом ярусе КС должна быть не меньше 7\. Длительность Т2 паузы между значениями сигналов L = 1 должна быть не меньше максимальной задержки сигналов в наименее быстродействующем ярусе КС. Быстродействующие конвейерные устройства строятся на триггерах Эрла (см. § 3.3), в которых преобразование информации производится во входной логике второго порядка. Конвейерная обработка информации находит широкое применение в векторных процессорах [9]. г,

I Рис. 6.147 Рис. 6.148 При первом запуске конвейера обработанная информация появляется на его выходе через время тп • (Ti + Т2), где тп - число ступеней конвейера, а в дальнейшем выходная информация будет изменяться через время Т\ + Т2 (входная информация конвейера при этом также должна изменяться через время Т\ + Т2). Таким образом, скорость обработки однотипной информации определяется быстродействием только одной ступени конвейера. На рис. 6.148 показана структурная схема однофункцио-нального конвейерного устройства, в каждой ступени которой имеются сигналы, поступающие на РП без преобразования в КС. Если задержка сигналов в КС равна г, то для сигналов, не проходящих через КС, следует ввести задержку на время г, что обычно производится введением "холостой" логики, не производящей преобразования информации. Многофункциональные конвейеры кроме входов данных имеют управляющие входы, с помощью которых перестраивается структура конвейера на выполнение различных функций. На перестройку конвейера обычно требуется время, не меньшее m-(T!+T2). Конвейеризация обработки данных используется в некоторых БИС и СБИС для увеличения скорости их работы. Фирма Weitek в 1983 г. выпустила набор СБИС с конвейерной обработкой данных, в частности, СБИС WTL1Q32 для умножения 32-разрядных чисел с плавающей точкой, имеющую быстродействие 10 Мфлопс (107 операций с плавающей точкой в секунду; флопс - Floating Point Operations per Second) [28]. Конвейерный быстрый умножитель. На рис. 6.149 показана первая ступень конвейерного умножителя 12 х 8 разрядов, построенная на 12 ИС 555ИП8. Эта ступень производит вычисление четырех частичных произведении и фиксацию их значений сигналом L во внутренних триггерах ИС (см. § 6.13). Остальные ступени конвейерного умножителя показаны на рис. 6.150 (квадратами обозначены одноразрядные сумматоры, прямоугольниками - триггеры, подключенные к выходам сумматоров, и шестиугольниками - триггеры с входной "холостой" Уо" У," х -1 о 1 2 3 ~ -1 о 1 Н l MPL 2э УП У2 Уз"! ми. х - У. Уз MPL Уз~ Ут X -1 0 1 2 3 т -1 о 1 MPL Л- Уо- у,- Гх -1 о 1 2 3 т -1 о 1 -Н i MPL 2в хв-27 у,-у2- Уэ MPL 2 *з~ 2е *Н -z * Уэ-\ У* Уз MPL a о i 2 з 4ф MPL Уо- у,- х -1 о 1 2 3 Т -1 о 1 Н L MPL 2е х7 ily.H-i у2- У: MPL 0 1 з 4

Уз- у6-y,- t Г- 12 х..Н 7э 7< дз 11 Уз~ Уе Ут X -1 о 1 2 3 Т -1 О 1 MPL a о i г з 4Ф Г f1 У,-Г&1 Г y*~i J 1 Уэ" Уэ-1 У4- Уз" у7- 0 ... 92 93 94 95 96 97 98 ... 119 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||